ADS 2017由美国Agilent公司推出(现在应该叫是德科技 Keysight Technologies )的微波电路和通信系统仿真软件,是当今业界最流行的微波射频电路、通信系统、RFIC设计软件;也是国内高校、科研院所和大型IT公司使用最多的软件之一。其功能非常强大,仿真手段丰富多样,可实现包括时域和频域、数字与模拟、线性与非线性、噪声等多种仿真分析手段,并可对设计结果进行成品率分析与优化,从而大大提高了复杂电路的设计效率,是非常优秀的微波射频电路、系统信号链路的设计工具。主要应用于:射频和微波电路的设计,通信系统的设计,RFIC设计,DSP设计和向量仿真;是射频工程师必备的工具软件。Advanced Design System (ADS)先进设计系统是领先的电子设计自动化软件,适用于射频、微波和信号完整性应用。ADS 是获得商业成功的创新技术(例如 X 参数*和 3D 电磁仿真器)的代表,这些技术已被无线通信与网络以及航空航天与国防领域中的领先厂商广泛采用。对于 WiMAX 、LTE、多千兆位/秒数据链路、雷达和卫星应用,ADS 能够借助集成平台中的无线库以及电路系统和电磁协同仿真功能提供基于标准的全面设计和验证。 闪电小编这里带来的是 ADS 2017最新完整安装包,内涵授权激活文件,可以完美激活 ADS 2017!

、LTE、多千兆位/秒数据链路、雷达和卫星应用,ADS 能够借助集成平台中的无线库以及电路系统和电磁协同仿真功能提供基于标准的全面设计和验证。 闪电小编这里带来的是 ADS 2017最新完整安装包,内涵授权激活文件,可以完美激活 ADS 2017!

ADS2017 功能特色

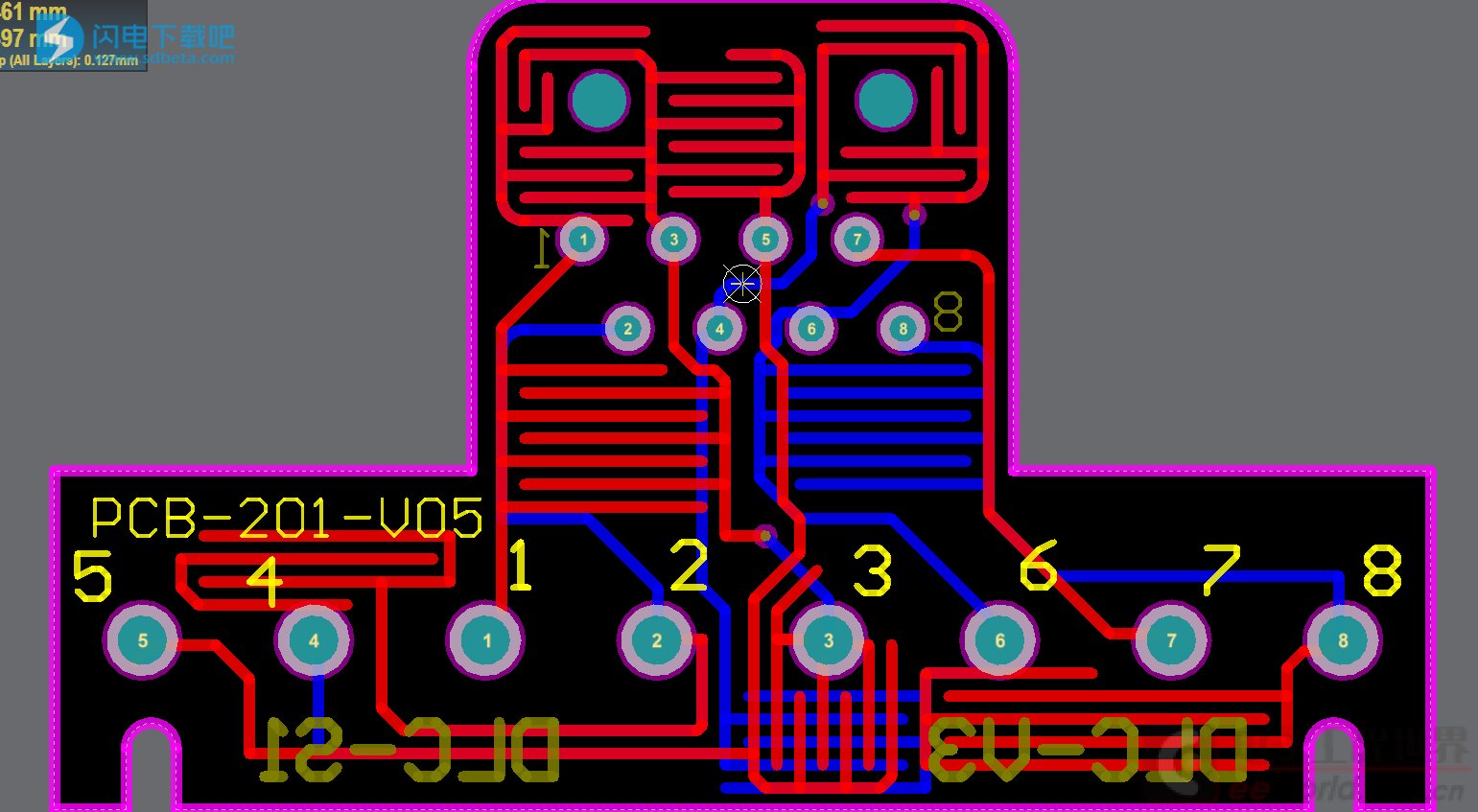

先进设计系统是领先的电子设计自动化软件,适用于射频、微波和信号完整性应用。ADS 是获得商业成功的创新技术(例如 X 参数*和 3D 电磁仿真器)的代表,这些技术已被无线通信与网络以及航空航天与国防领域中的领先厂商广泛采用。对于 WiMAX 、LTE、多千兆位/秒数据链路、雷达和卫星应用,ADS 能够借助集成平台中的无线库以及电路系统和电磁协同仿真功能提供基于标准的全面设计和验证。

、LTE、多千兆位/秒数据链路、雷达和卫星应用,ADS 能够借助集成平台中的无线库以及电路系统和电磁协同仿真功能提供基于标准的全面设计和验证。

快速、精确、简单易用的全套集成系统、电路和电磁仿真器,能够一次性成功完成桌面流程设计。

特定应用设计指南将长期积累的专业知识应用于简单易用的界面中。

领先的行业和代工合作伙伴可专门或比其他产品优先数个月为 ADS 提供支持。

- 完整的原理图设计和布局或电路布局

- 领导电力,电子和电信行业的最新技术

- 具有完整的所需部件类型库,例如晶体管,源极,二极管,传输线和...

- 能够设计各种模拟和数字滤波器

- S参数和X参数的线性模拟和分析

- 射频系统模拟器(RF)

- 交流和直流直流分析

- 能够使用13个优化工具优化电路性能

- 功率放大器的分析

- 计算和模拟晶体管的工作点

- 可以比较各种参数的输出数据的图形和数字显示

- 能够与史密斯图表一起工作

- 使用谐波平衡和谐分析

- 研究和计算MOSFET或金属氧化物半导体场效应晶体管(MOSFET)色散参数

- 瞬态分析或瞬态分析

- 计算动量或动作大小(动量).

主要特性与技术指标

ADS 2017 为充满挑战的无线通信设计提供了 3D 解决方案和更多解决方案,其中包括:

-

3D 版图查看、路由选择和编辑

-

多技术 3D 电热仿真

-

利用 Python 数据链路进行 3D 数据可视化

-

使用 FEM 进行更强大的 3D 电磁仿真

-

3D Via Designer:支持访问精确的过孔模型

-

自动建立线圈等器件的 PCell 结构

-

用于分层管理的新选件

-

改善的互操作性

-

SOA 支持更好的可靠性

-

增强的电路仿真性能

ADS2017安装与破解

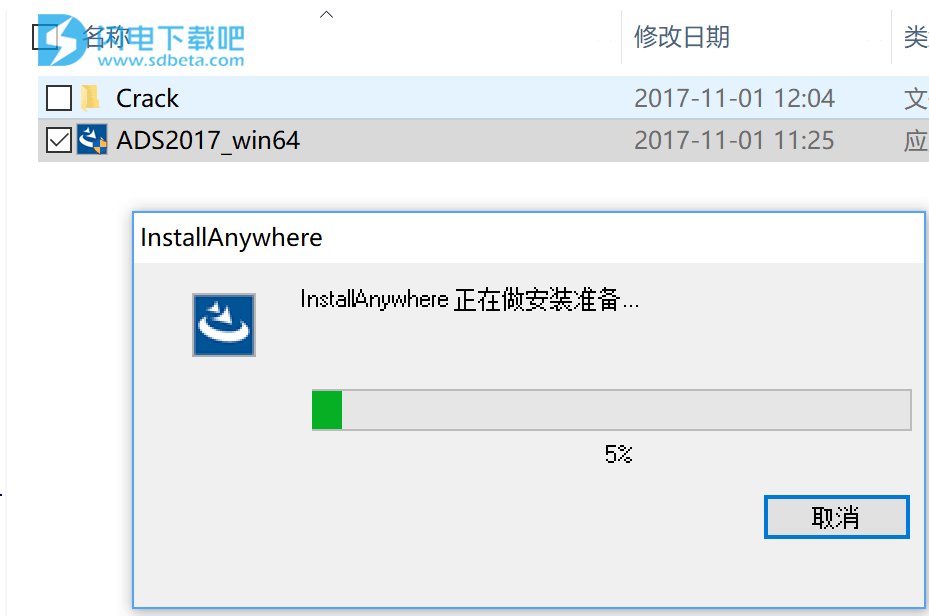

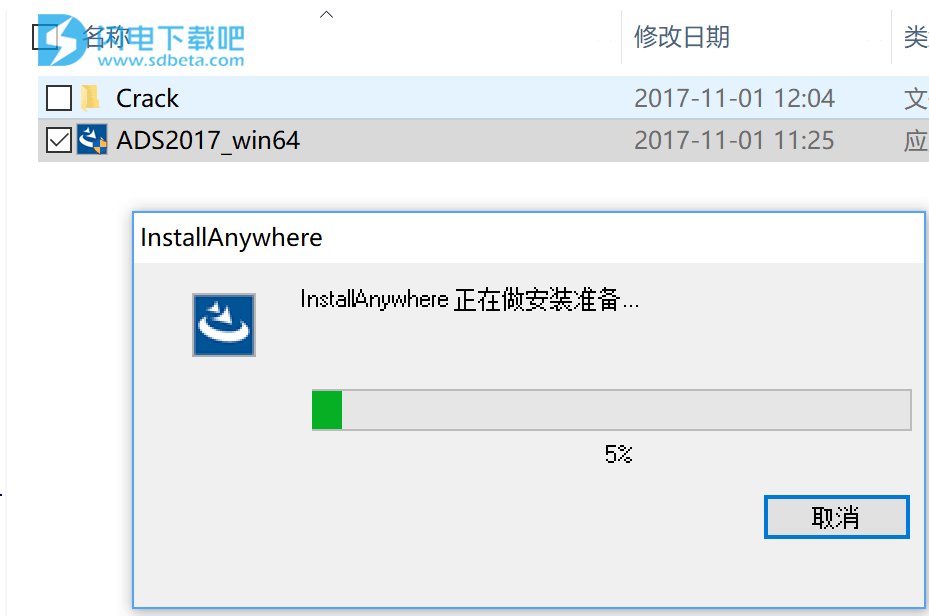

1.本站下载压缩包,解压后双击ADS2017_win64.exe安装,耐心等待解压安装包

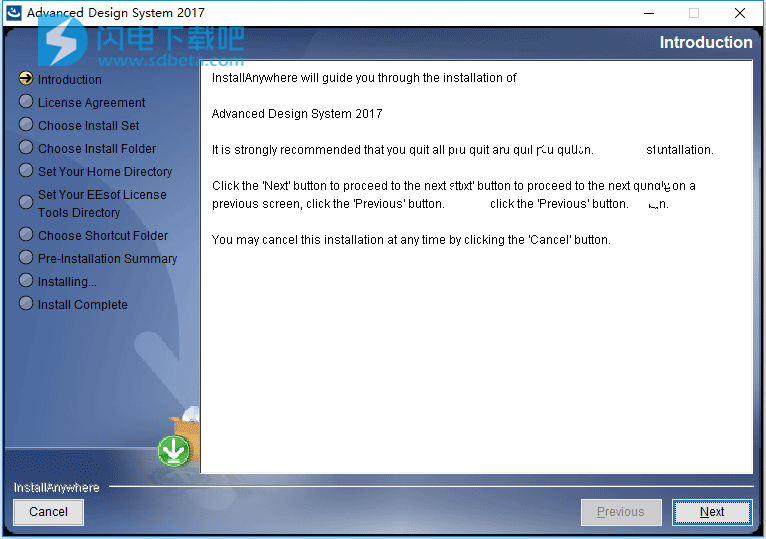

2.点next继续,按照提示完成安装

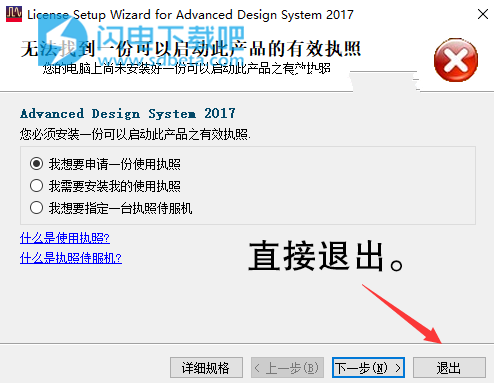

3.软件安装完成后,关闭许可证安装向导窗口

4.复制“EEsof_License_Tools”文件夹到许可证工具安装目录替换原文件夹,默认的路径

C:\Program Files\Keysight\EEsof_License_Tools

5.根据自己电脑的位数,复制ADS2017文件夹,到软件安装路径替换原文件夹。默认路径:

C:\Program Files\Keysight\ADS2017

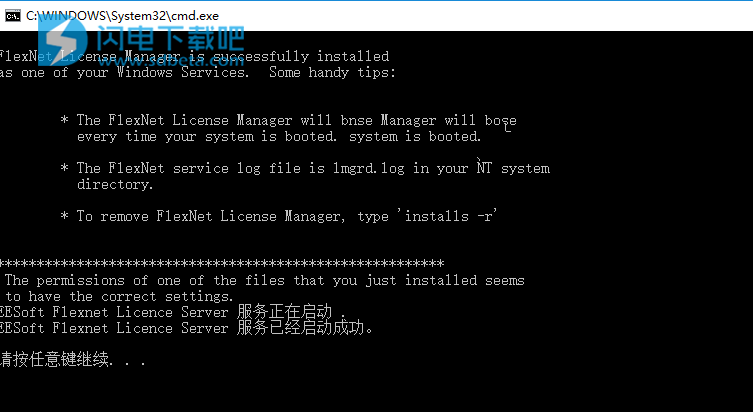

6.替换之后,找到“EEsof_License_Tools\bin\win32”,右键管理员身份运行”server_install.bat”安装服务

7.服务安装成功之后,双击”注册.reg”添加注册表。

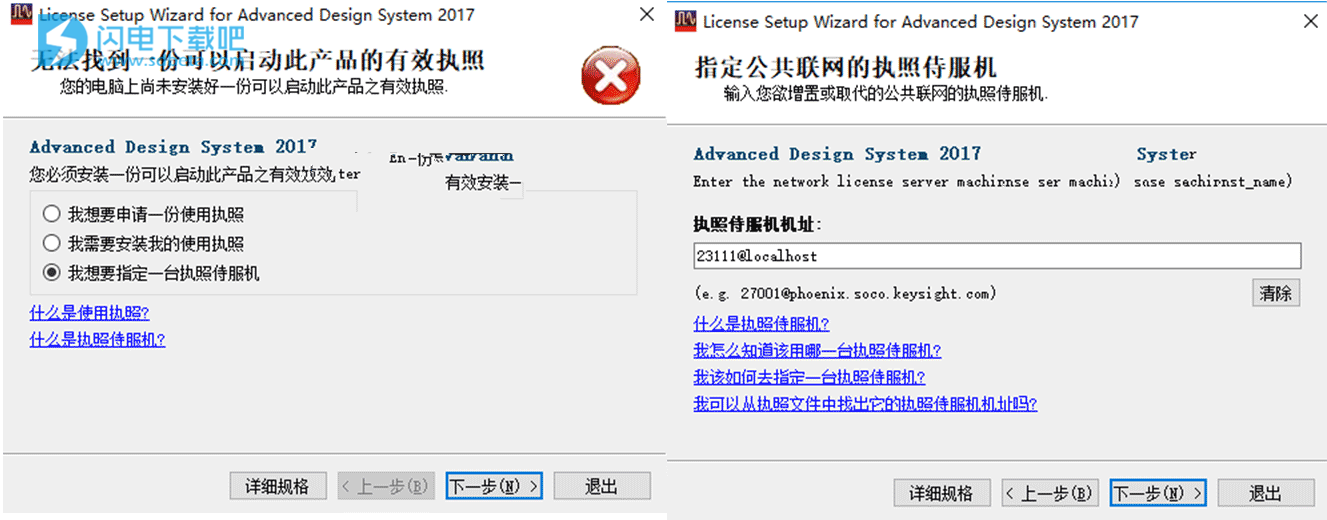

8.打开软件,在许可证配置界面,选择“我想要指定一台执照伺服机”,输入“23111@localhost”。如图:

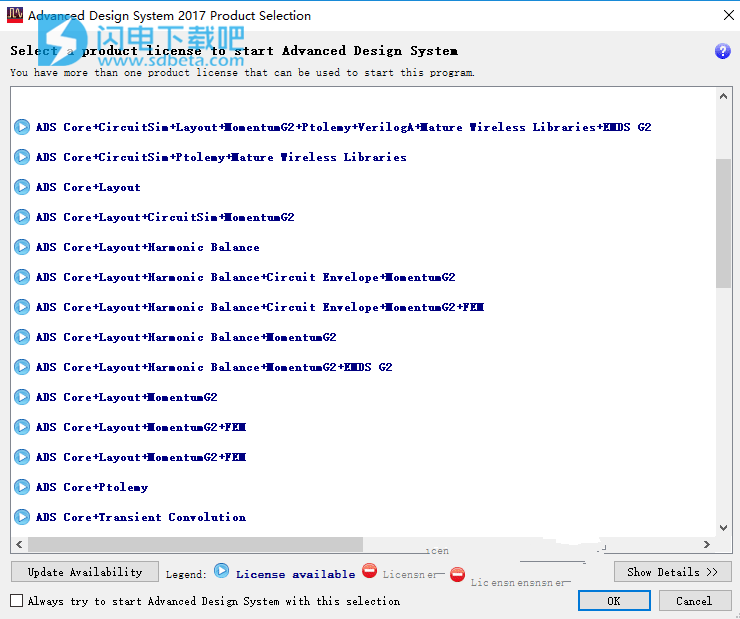

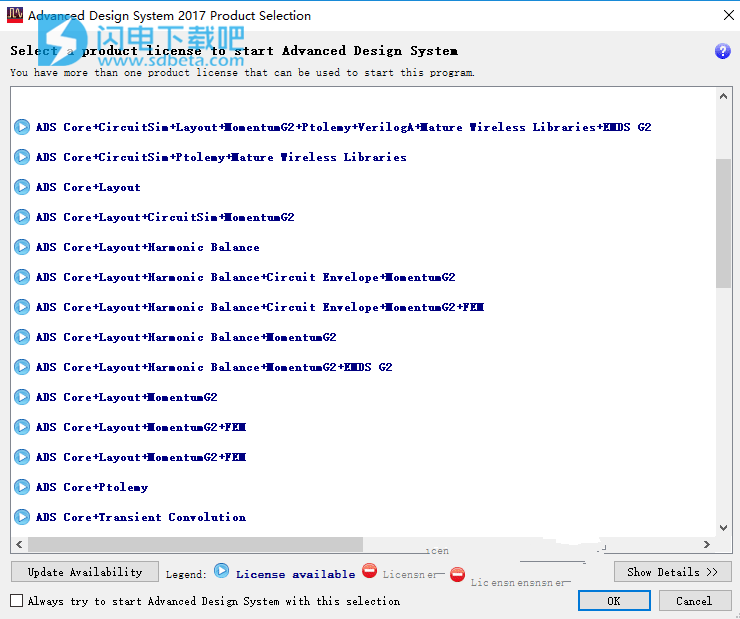

9.打开软件,选择相关的许可,启动软件即可。

10.破解完成,所有功能都可以免费使用了!

高级设计系统2017更新版本说明

安装说明

与其他ADS次要更新不同,ADS 2017 Update 0.2不是一个插件,而是一个完整的安装程序。在安装ADS 2017 Update 0.2之前,它将卸载以前安装的任何ADS 2017(发货或更新0.1),然后为Update 0.2执行全新安装。有关更多信息,请参阅ADS 2017 Update 0.2安装说明文档。

平台支持

支持的平台: Windows和Linux 64位。

问题解决

ADS 2017 Update 0.2解决了与电路仿真,数据显示,设计编辑,设计和技术管理,EM集成,IC设计流程和 SIPro / PIPro相关的问题。

电路仿真

HiCUM v2.33模型现在在扫描设计参数时重新评估。

修复了ADS和Spectre之间SP和SP噪声(nfmin)中的结果不匹配问题。

修复了删除SnP文件关闭Touchstone Combiner窗口的问题。

您现在可以打开Tx_AMI上的AMI选项卡并加载AMI文件,并查看所有AMI参数。

修复了导入IBIS模型文件时发生的崩溃。

不允许出现错误消息“[算法模型]子参数(null)...”不再显示。

包含Global Foundries设备的基于网表的模拟现在报告NFmin的非零值。

解决了ADS解析器报告GF 22nm V1.2.0型号不支持的操作符和语法错误的问题。

电路包络模拟现在更加精确和快速,它可以用两种时间步长模拟电路。

修正了Hspice网表模式下HiSIM HV的行为。

将“禁用”按钮添加到数据显示窗口。

数据显示

即使在重新启动ADS会话之后,新的自定义工具栏现在仍可见。

禁用切换按钮将重新添加到缩放工具栏上。

设计编辑

捕捉垂直,水平和对角线的改进 - ADS 2017将鼠标捕捉到垂直,水平或与先前的点击布局相对的位置(45度)。在此之前,这可能会干扰捕捉针,顶点,中点等。在此更新中,鼠标将根据捕捉首选项捕捉到针,顶点,中点,圆/弧中心和交点,即使这些点不是在上一次鼠标点击的垂直,水平或对角线上。如果捕捉点位于前一次鼠标单击的垂直线,水平线或对角线上,鼠标将捕捉到边线和中心线(如果设置了该首选项)。

修复了崩溃时在布局窗口中删除边缘引脚的长度。

添加了API 来检查和设置库技术互操作性模式。

关闭Via定义对话框时删除了警告消息“Antipad SameAsKeepout not implemented”。

修复了制造网格错误,其中将制造网格设置为0.05um后,路径移动了0.075um距离,因为形状本应移动到0.05um距离。

设计和技术管理

对于可互操作的组件,基于视图名称的SimInfo搜索现在将默认采用幽灵模拟。如果所选视图名称在CDF中没有匹配的SimInfo部分,我们会寻找一个幽灵SimInfo部分。如果要覆盖此行为,可以在$ HOME / hpeesof / config / de_sim.cfg文件中设置变量DefaultSimInfoName。如果您不想要任何默认值,请将名称设置为None(与SimInfo名称不匹配)。

基材现在列在ADS主窗口的文件夹视图中。

修复了EditStackupDialog从没有技术的引用库中检索信息时的崩溃。

添加了AEL API来检查和设置库技术互操作性模式。

添加了适用于自定义表单集的 dm_get_formset_form_names()函数。

示例和设计指南

修复了$ HPEESOF_DIR \ examples \ Behavioral_Models \ Verilog-A_and_AMS下的发货范例'VAMS_Examples_wrk'的许可证问题 。

EM集成

修复了可互操作的电路/ EM协同流程中的端口设置。在EM模拟的辅助单元视图中('..._ emCosim:layout'),连接到相同电路组件项的所有引脚将在相应的端口设置中组合在一起。这样可以减少EM仿真中的端口数量,而不会影响精度。

FEM

修正边缘引脚略大于几何边缘时的错误(开路)结果。

改进和增强了分布式有限元模拟。

减少了具有多个端口的大型设计的内存消耗,这可能会导致仿真时间增加10-15%,具体取决于机器和设计。

通过设计师

修复了几何不能正确更新的问题。

IC设计流程

LVS

改进复杂的非同步设计的网络映射。

使用选项组件映射参数值运行批处理LVS。

运行批次LVS并关闭选项“检查网络名称”。

改进无效设置的错误消息。

刚果(金)

当技术是只读而不触发版本控制活动时加载结果。

突出显示错误而不修改主布局设计。

显示对话框时显示指定作业的结果。

扩大芯片面积以包括超大尺寸和补偿值。

作业名称下拉现在列出作业名称中有点的作业。

默认的圆圈分辨率现在设置为5度。

在不同的标题下显示固定错误。

添加自动选择复选框。

Assura DRC链接

按错误消息和输出层分组DRC错误。

IP编码器

修复了编码网表给出“视图名称未指定”错误的问题。

信号完整性/电源完整性(SIPro / PIPro)

PIPro schemaitc测试平台的创建现在可以与最新更新的Murata adslibrary版本1707一起正常工作。

如果lib.defs 包含ADS设计工具包的无效路径,SIPro / PIPro安装程序现在可以正常打开 。

SIPro / PIPro单元名称不允许特殊字符,如*()[] {} / ?!,;:'“|。

修复了SIPro / PIPro原理图中的特殊字符处理。

对于具有多个端口和组件的大型设计,可减少SIPro或PIPro-AC仿真的内存消耗,这可能会导致仿真时间增加10-15%,具体取决于机器和设计。

、LTE、多千兆位/秒数据链路、雷达和卫星应用,ADS 能够借助集成平台中的无线库以及电路系统和电磁协同仿真功能提供基于标准的全面设计和验证。 闪电小编这里带来的是 ADS 2017最新完整安装包,内涵授权激活文件,可以完美激活 ADS 2017!

、LTE、多千兆位/秒数据链路、雷达和卫星应用,ADS 能够借助集成平台中的无线库以及电路系统和电磁协同仿真功能提供基于标准的全面设计和验证。 闪电小编这里带来的是 ADS 2017最新完整安装包,内涵授权激活文件,可以完美激活 ADS 2017! 、LTE、多千兆位/秒数据链路、雷达和卫星应用,ADS 能够借助集成平台中的无线库以及电路系统和电磁协同仿真功能提供基于标准的全面设计和验证。

、LTE、多千兆位/秒数据链路、雷达和卫星应用,ADS 能够借助集成平台中的无线库以及电路系统和电磁协同仿真功能提供基于标准的全面设计和验证。