Questa Advanced Simulator破解版是一款功能强大的FPGA和SoC芯片模拟,测试和调试工具,使用旨在将高性能和容量模拟与统一的高级调试功能相结合,为Verilog,SystemVerilog,VHDL,SystemC,PSL和UPF提供最完整的本机支持。 Questa高级仿真器是Questa验证平台的核心仿真和调试引擎; 该综合先进的验证平台能够降低验证复杂FPGA和SoC设计的风险。Questa通过RTL,门和晶体管从TLM(事务级建模)跨越复杂SoC和FPGA设计和验证所需的抽象级别,并且对多种验证方法(包括基于断言的验证(ABV),开放验证方法( OVM)和通用验证方法(UVM)来提高测试平台的生产力,自动化和可重用性。硬件描述语言很多如Verilog,SystemVerilog的,VHDL,SystemC的方案,PSL和UPF支持,并与不同的工具,让您测试上面设计可编程芯片并实现真正的报价的可能性目录。Questa模拟器实际上是Questa综合评估平台模拟和调试的核心,可以降低评估芯片的风险。本次小编带来的是Mentor Graphics Questa Sim SE 10.4e 破解版,含破解文件和详细的安装破解激活图文教程,需要的朋友不要错过了!

安装破解教程

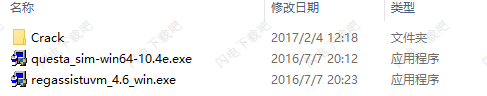

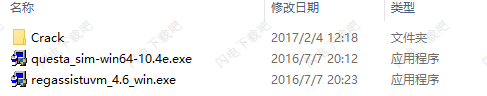

1、在本站下载并解压,如图所示,得到questa_sim-win64-10.4e.exe安装程序和Crack破解文件夹

2、双击questa_sim-win64-10.4e.exe运行,如图所示,稍等片刻

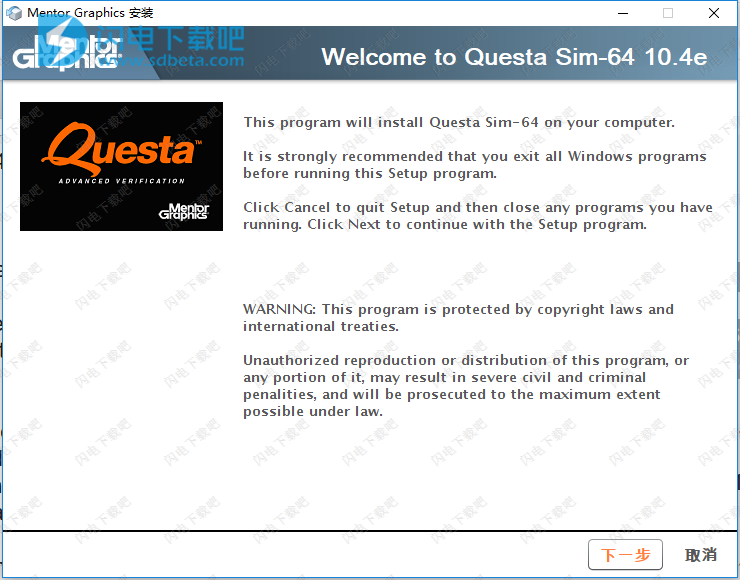

3、点击下一步

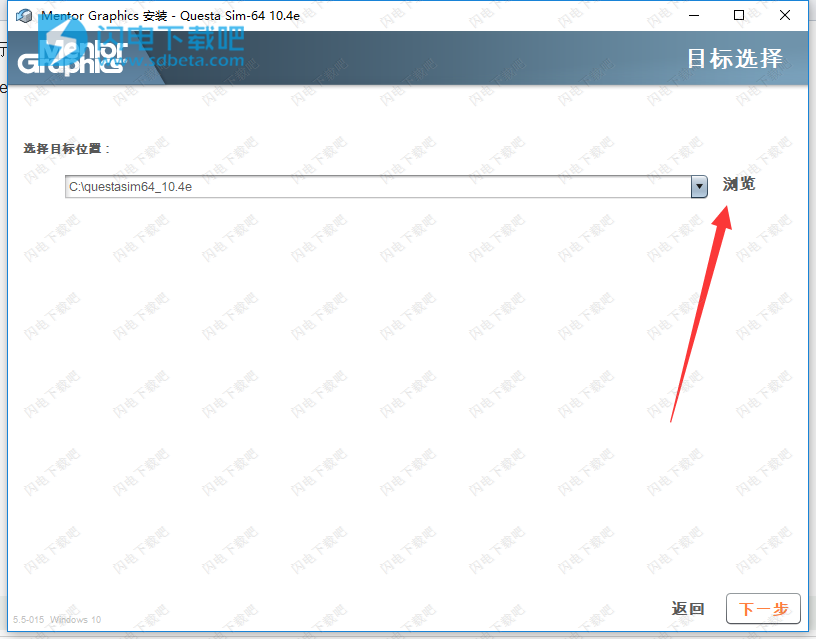

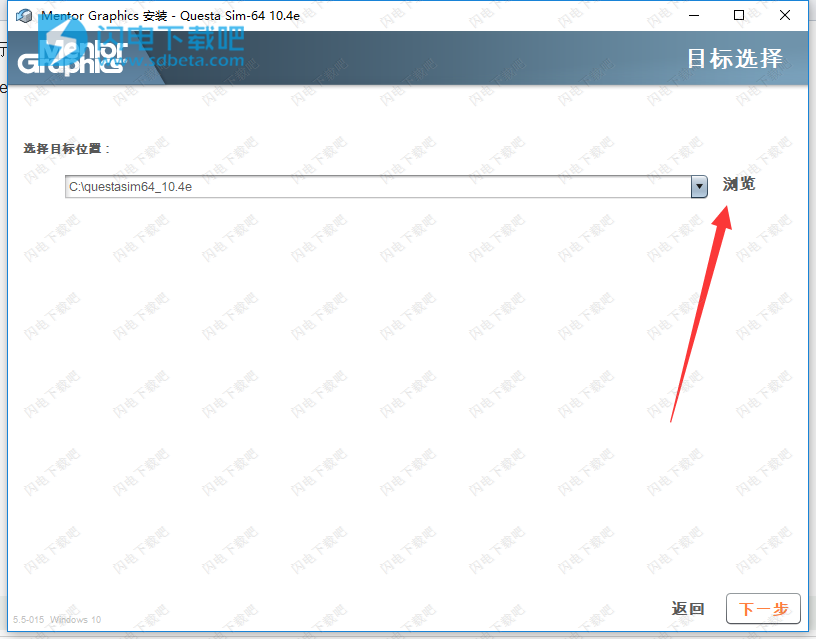

4、点击浏览选择软件安装路径,注意路径中不要有中文,点击下一步

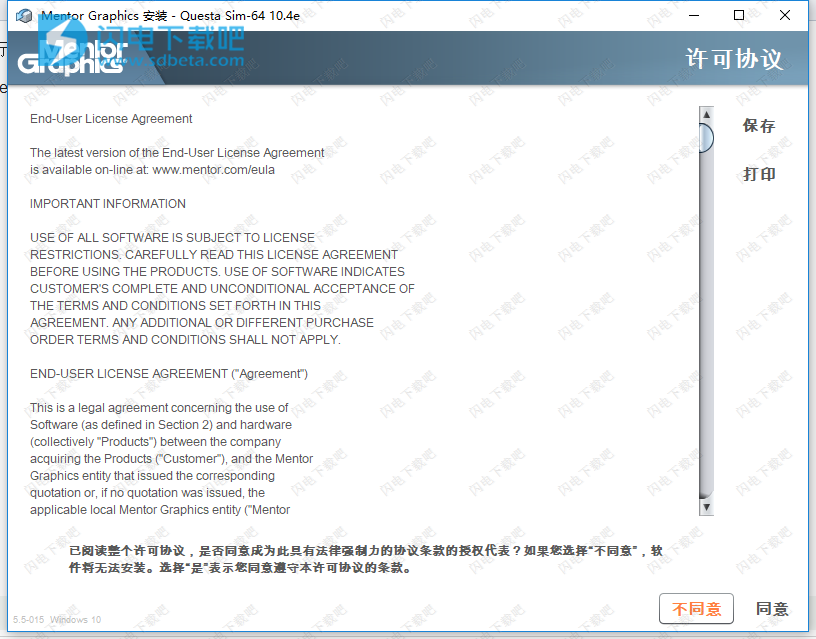

5、许可协议,点击同意

6、安装中,大家耐心等待几节课

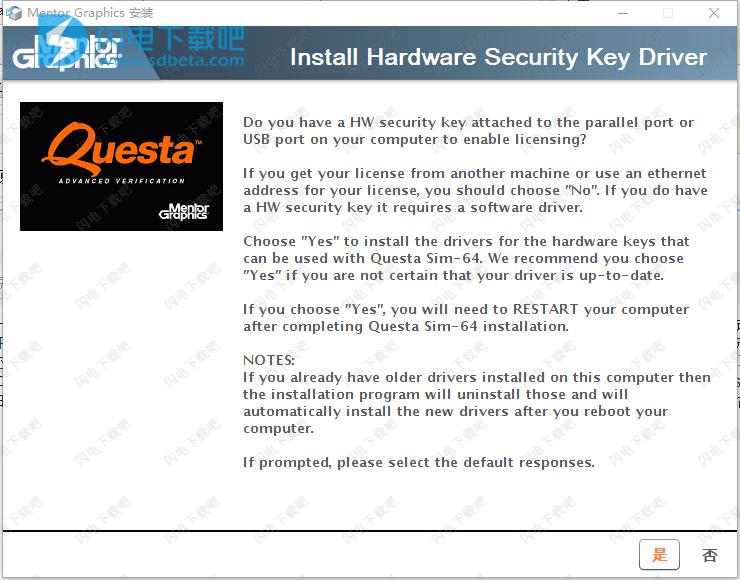

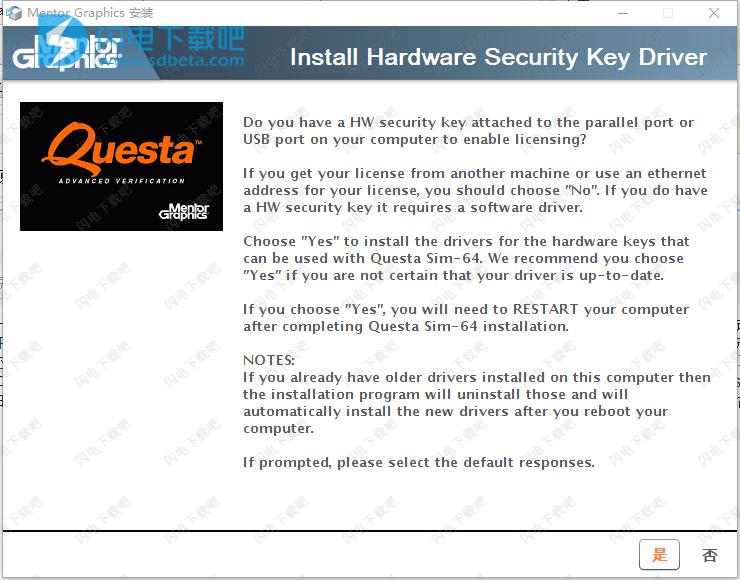

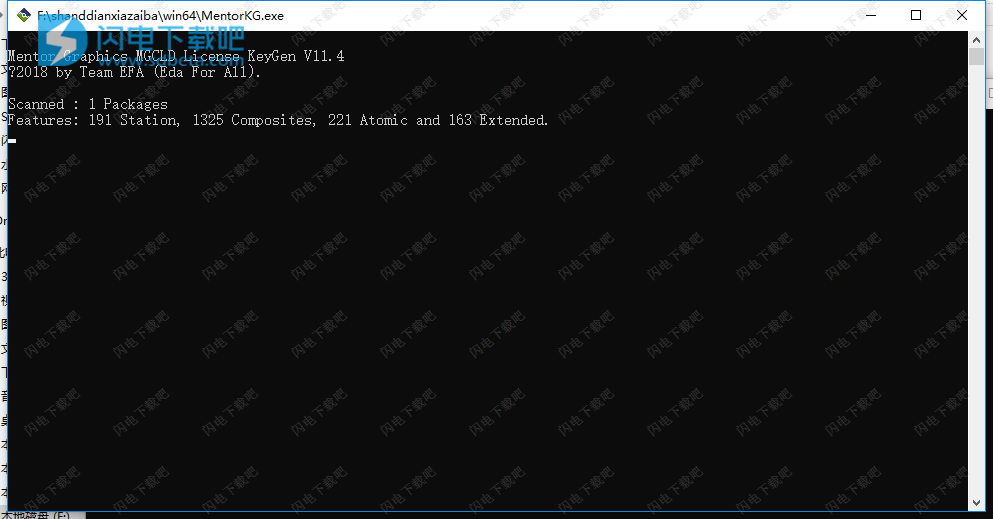

7、安装完成,退出向导,注意不要安装key drivers

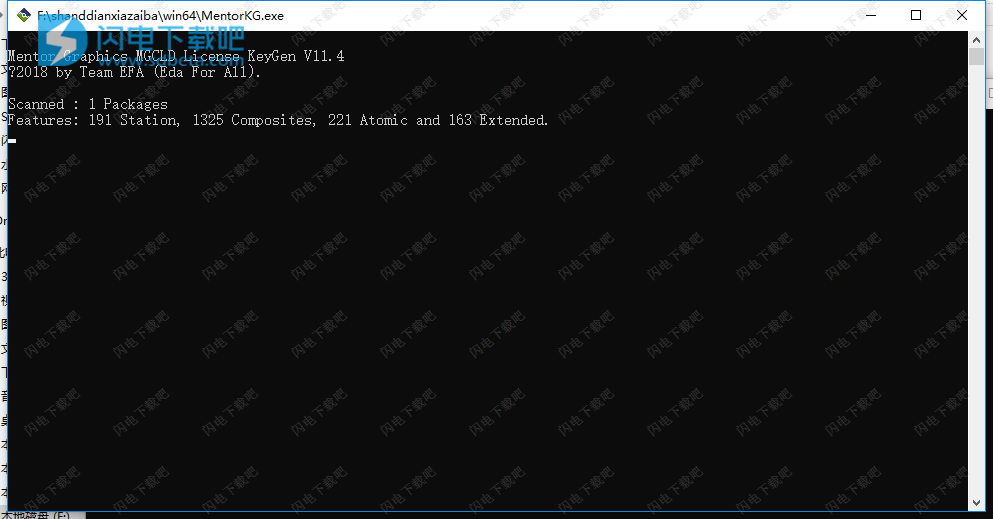

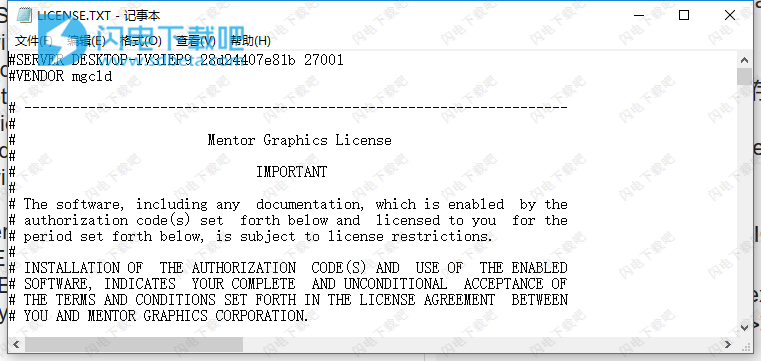

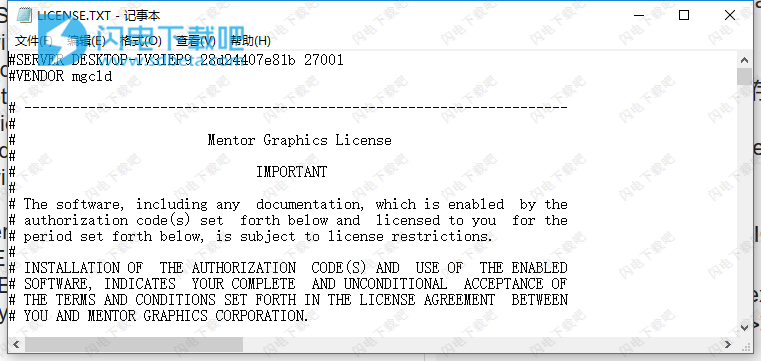

8、安装完成后不要运行软件,将Crack破解文件夹中的patch64_dll.bat和MentorKG.exe复制到软件安装目录中win64文件夹下,以防止丢失,运行patch64_dll.bat,将生成的许可证另存为lic_modelsim.txt,保存在软件安装目录下(避免误删除)

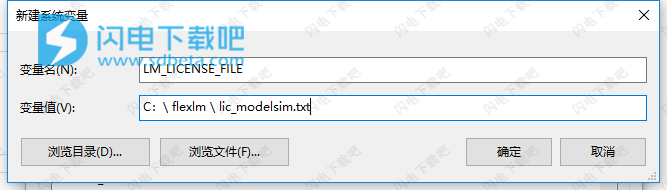

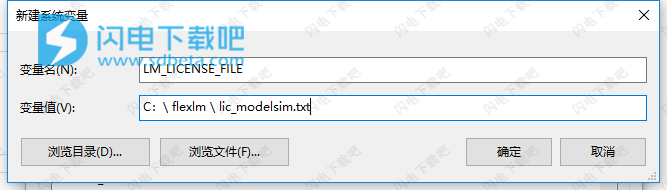

9、以上操作完成后,创建一个系统环境变量,(控制面板 - >系统 - >高级 - >环境变量),LM_LICENSE_FILE并将其指向一个文件: LM_LICENSE_FILE,C:\ flexlm \ lic_modelsim.txt,运行软件

功能特色

1、硬件描述的高效率和多语言支持

2、高效和先进的评估

3、易于使用和快速调试

4、自动测试生产

5、多核模拟和并行测试

软件特色

图的列表

QuestaSIM的操作结构和流程

工作库

编译设计

创建一个加密信封

加密信封包含要保护的设计数据

加密信封包含`包含编译器指令

使用vlog+protect编译后的结果

Verilog/SystemVerilog加密使用流程

用用户定义的宏提供IP代码

通过保护编译器指令来提供IP

创建项目对话框

项目窗口细节

将项目添加到项目对话框

创建项目文件对话框

将文件添加到项目对话框

在项目窗口中右键单击编译菜单

单击加号显示设计层次结构

设置编译顺序

分组文件

添加模拟配置对话框-设计选项卡

结构窗口与项目

项目窗口概述

添加模拟配置对话框

项目窗口中的仿真配置

添加文件夹对话框

指定一个项目文件夹

项目编译器设置对话框

指定文件属性

项目设置对话框

创建一个新库

工作区中的设计单元信息

编辑库映射对话框

具有相同名称的子模块

导入库向导

VHDLDelta延时过程

致命信号分段违例(SIGSEGV)

当前发生错误的过程

指示代码停止执行的蓝色箭头

本地窗口中的空值

类树窗口中的类

类图窗口中的类

结构窗口中的类

类实例窗口

将类实例放置在Wave窗口中

波形窗口中的类信息弹出窗口

在监视窗口中查看课程

显示细粒度分析结果的容量窗口。

波形窗口中的类路径表达式

/top/a演员为c1和c1prime

将c1投射到c1prime

类类型的扩展

垃圾收集器配置

结构窗口显示UVM层次结构

扩展的UVM宏

UVM细节窗口流模式

UVM详细信息窗口ConfigDB模式

UVM细节窗口序列模式

使用UVM组件处理窗口层次结构模式

UVM消息查看

波形窗口中的UVM事务流

GUI中的SystemC对象

SystemCSource中的断点

设置允许库步骤功能

SystemC对象和进程

汇总数据显示在波形窗口中

波形窗口中的交易剖析

波形窗口中的交易流

查看事务和属性

并行并行交易

波形窗口中的交易-查看

事务流属性

改变属性的外观

列表窗口中的事务

对象窗口中的事务

录制事务

Questa验证在不同抽象层次上的IP交易

对象窗口中的数组

Questa在波形窗口中验证IP交易

波形窗口中的并发事务重叠

Questa验证IP阵列(2X2)在WaveWindow中

数组的颜色

Questa在对象窗口中验证IP对象

Questa在列表窗口中验证IP对象

查看Questa验证IP关系

交易窗口-数据选项卡

交易窗口-关系选项卡

在波形窗口中显示两个数据集

数据集快照对话框

打开数据集对话框

结构选项卡

数据集浏览器

橙色钻石指示的虚拟对象

波窗口

插入点栏

网格和时间线属性

波窗口光标的原始名称

同步所有活动游标

光标链接菜单

配置光标链接对话框

带有折叠事件和增量时间的波形窗格

具有特定时间的扩展时间的波形窗格

未记录事件的波形窗格

扩展时间范围内的波形窗格

书签属性对话框

波形信号搜索对话框

表达式生成器对话框

为表达式生成器选择信号

“波形窗口首选项”对话框的“显示”选项卡

“波形窗口首选项”对话框的“网格和时间线”选项卡

波窗口时间轴中的时钟周期

波形格式菜单选择

波形属性对话框的格式选项卡

改变信号基数

波形窗口中的全局信号基数对话框

独立的信号与波窗口分频器

分裂波窗玻璃

红钻表示的波群

贡献信号小组

保存格式对话框

游标之间的波形保存

波形过滤器对话框

波形过滤器数据集

在波形窗口中添加类对象

波形窗口中的类信息弹出窗口

添加到波形窗口的虚拟接口对象

信号组合创建虚拟总线

WaveExtract/PadBus对话框

虚拟信号生成器

虚拟信号生成器帮助

创建一个虚拟信号。

波形窗口中的虚拟信号

修改断点对话框

信号断点对话框

源窗口中的断点

文件断点对话框

波形比较向导

启动比较对话框

比较工作区窗格中的选项卡

结构浏览器

按区域添加比较对话框

比较方法选项卡

为定时比较添加时钟

波形比较选项

查看波形差异

使用帮助

1、文件和地图库

你需要几个文件来模拟QuestaSIM的设计。

设计文件(VHDL和/或VerilogVHDL,Verilog和/或SystemC),包括刺激设计。

图书馆,工作和资源。

modelsim.ini文件(由库映射命令自动创建)。

有关在系统启动期间访问的文件(包括modelsim.ini文件),初始化序列和系统环境变量的详细信息,请参阅“系统初始化”附录。

2、什么是图书馆?

库是QuestaSIM存储要用于模拟的数据的文件系统上的位置。在模拟需要数据之前,QuestaSIM使用一个或多个库来管理数据的创建。库也有助于简化模拟调用。

您可以通过以下方式使用库。

作为包含您设计的编译版本的本地工作库

作为资源库

3、资源库

资源库通常不变,并且可用作设计的部件源。您可以创建自己的资源库,也可以由其他设计团队或第三方提供(例如,硅片供应商)。

资源库的示例:

在您的小组内共享信息

供应商库

包

以前编译过的自己的工作设计元素

QuestaSIM不是每次模拟时都编译所有设计数据,而是使用安装树中提供的预编译资源库。使用预编译的库有助于减少编译和模拟启动期间的错误。此外,如果您对单个Verilog模块进行更改,则QuestaSIM仅重新编译该模块,而不是设计中的所有模块。

4、将逻辑工作映射到物理工作目录

VHDL使用可以映射到Questa SIM库目录的逻辑库名称。 如果库的映射不正确,并且您调用了仿真,则不会加载必要的组件,仿真将失败。 同样,编译也可以依赖于正确的库映射。

默认情况下,Questa SIM可以在当前目录中找到库(假设它们的名称正确),但是为了找到位于其他位置的库,您需要将逻辑库名称映射到库的路径名。

5、 第1步-创建工作和资源库

在编译源文件之前,必须使用vlib命令创建一个工作库,以在其中存储编译结果。工作库的内容将随着您更新设计和重新编译而改变。

Vlib默认创建一个“平面”库类型。与传统库类型相比,平面库将库信息压缩成一小部分文件。这可以解决非常大型的库所带来的性能和容量问题。

vmake命令不支持平面库类型,当您执行以下任何操作时,需要vmake命令的流程可以恢复为旧式库类型:

在vlib命令中指定“-typedirectory”。

将modelsim.ini文件中的DefaultLibType变量设置为值0。

将shell环境变量MTI_DEFAULT_LIB_TYPE设置为值0。

如果路径包含多个需要转义的项目,例如路径名中的空格或反斜杠字符,请使用大括号({})。例如:

vmapcelllib{$LIB_INSTALL_PATH/DocumentsAndSettings/All/celllib}

先决条件

了解包含设计文件和资源库的目录的路径。

启动QuestaSIM

程序

选择“文件”>“更改目录”以打开“浏览文件夹”对话框。

导航到源文件所在的目录。

使用vlib命令以下列方式之一创建逻辑工作库:

在UNIXshell或“脚本”窗口中输入vlib命令:

vlib工作

文件>新建>库“。

使用vmap命令在逻辑库名称和目录之间映射一个或多个用户提供的库:

vmap<logical_name><directory_pathname>

创建一个名为work的库,将其放置在当前目录中,并在Structure窗口中显示工作库(图1)。

第2步-编译设计

收集设计文件并创建工作目录后,编译设计。您必须根据用于编写设计代码的编程语言选择适当的编译器命令。

Verilog和SystemVerilog-用vlog命令编译。

VHDL-用vcom命令编译。

SystemC-用sccom命令编译。

先决条件

创建工作库并将所需的资源库映射到工作库。有关更多信息,请参阅步骤1-创建工作和资源库。

SystemC设计需要安装gcc编译器。有关更多信息,请参阅编译SystemC文件。

程序

根据用于创建设计的语言,您将使用以下QuestaSIM命令之一来编译设计:

如果您的源文件被写入...

Verilog和/或SystemVerilog

在Transcript窗口中输入以下内容...

您可以按任何顺序编译Verilog文件,因为它们不依赖于顺序。 例如:vlog gates.v和2.v cache.v memory.v

如果您的源文件被写入VHDL

在Transcript窗口中输入以下内容...

VHDL单元按它们在命令行上出现的顺序进行编译。 对于VHDL,编译顺序很重要 - 您必须在引用它们的体系结构之前编译任何实体或配置。 项目可以帮助您确定编译顺序。 例如:vcom v_and2.vhd util.vhd set.vhd

如果您的源文件被写入SystemC

在Transcript窗口中输入以下内容.

Questa SIM使用外部C / C ++编译器将SystemC源代码编译到工作库中,而sccom -link需要编译源代码并链接设计。 例如:

sccom -g basic.cpp

sccom -link

其中-g参数编译调试设计,并且-link参数在SystemC对象上执行最后的链接。

第3步-优化设计

优化是一个可选步骤,通过限制设计对象的可见性可以提高性能。QuestaSIM使用vopt命令执行全局优化。

先决条件

创建工作库并将所需的资源库映射到工作库。有关更多信息,请参阅步骤1-创建工作和资源库。

编译设计。请参阅步骤2-编译设计。

程序

在命令行中输入以下命令:

vopttop-otopopt

哪里:

top是编译的顶级模块的名称。

-otopopt指定设计优化版本的名称。

第4步-加载仿真设计

编译设计之后,需要使用任何顶层模块的名称(包含许多设计仅包含一个顶层模块)使用vsim命令加载设计。例如,如果您的顶级模块名为“testbench”和“globals”,则调用模拟器。

vsimtestbench全局变量

先决条件

创建工作库并将所需的资源库映射到工作库。有关更多信息,请参阅步骤1-创建工作和资源库。

编译设计。请参阅步骤2-编译设计。

程序

在命令行中输入以下命令:

vsimtestbench全局变量

testbench和globals是两个顶级模块。

在模拟器加载顶层模块之后,它会迭代加载设计层次结构中的实例化模块和UDP,并通过连接端口和解析分层引用将设计链接在一起。

注意:

通过将标准延迟格式(SDF)反标注文件应用于设计,您可以将实际延迟值合并到模拟中。

第5步-模拟设计

一旦成功加载设计,模拟时间将设置为零,并且您必须输入运行命令才能开始模拟。

您用来运行模拟的基本命令是:

添加波

BP

力

跑

步

向设计添加刺激

您可以通过多种方式为设计添加刺激。

基于语言的测试平台。

基于Tcl的QuestaSIM交互式命令。例如,force和bp。

VCD文件/命令。

第6步 - 调试设计

Questa SIM GUI提供了许多用于调试设计的命令,操作和窗口。 另外,您还可以使用命令行运行以下用于调试的基本模拟命令。