Xilinx软件开发套件(SDK)是一个集成开发环境(IDE),用于开发针对Xilinx嵌入式处理器的嵌入式软件应用。 SDK适用于使用Vivado®DesignSuite创建的硬件设计。 SDK基于Eclipse开源标准。SDAccel是一个OpenCL编程系统,是一款功能强大的开发环境。做为Xilinx SDx生态系统中的一员,为用户提供了一个编译器、一个调试器和一个分析器,SDAccel是首个面向OpenCL、C和C++进行架构优化的编译器,能够让开发者在FPGA上实现类似CPU/GPU的开发体验,例如编译、调试和优化等,例如其实现的FPGA数据中心加速服务相比CPU/GPU单位功耗性能提升了25倍,时延则缩短了50到70倍。SDAccel用于异构系统的C / C ++,在Xilinx FPGA上实现硬件加速器。 OpenCL是用于开发FPGA固件的C ++语言的应用之一。 SDAccel支持OpenCL,C和C ++内核的任意组合以及用于FPGA设计的库。该环境允许对中央处理器和FPGA加速器进行并行编程。

SDSoCM环境提供了使用标准编程语言开发和交付硬件加速嵌入式处理器应用程序的框架。它包括一个熟悉的嵌入式处理器开发流程,其中包含基于Eclipse的集成开发环境(IDE),嵌入式处理器应用程序的编译器以及在Xilinx的可编程逻辑资源上实现的硬件功能?设备。 sdscc / sds ++(称为sds ++)系统编译器分析程序以确定软件和硬件功能之间的数据流,生成片上特定于应用程序的系统,支持裸机,Linux和FreeRTOS作为目标操作系统。 sds ++系统编译器生成硬件IP和软件控制代码,自动实现数据传输,同步硬件加速器和应用软件,流水线通信和计算。使用Xilinx的SoC器件,例如Zynq-7000 SoC和Zynq UltraScale + MPSoC,您可以将应用程序的元素实现到硬件加速器中,运行速度比处理器上运行的优化代码快许多倍。与传统的CPU / GPU加速相比,Xilinx FPGA和SoC器件具有许多优势,包括能够实现可在处理器上运行的任何功能的定制架构,从而以更低的功耗实现更好的性能。要在Xilinx器件上实现软件加速的优势,您应该在硬件中加速应用程序的大型计算密集型部分。在自定义硬件中实现这些功能可以实现性能和功耗之间的理想平衡。 SDSoC环境提供工具和报告,用于分析嵌入式处理器应用程序的性能,并确定加速机会的位置。这些工具还提供缓存,内存和总线利用率的自动运行时检测,以跟踪硬件上的实时性能。硬件加速应用程序的开发人员可以利用熟悉的以软件为中心的编程工作流程来充分利用FPGA加速,而无需先前的FPGA或硬件设计经验。作为软件程序员,调用硬件功能与调用软件功能相同,让编译器实现硬件/软件分区。但是,开发人员还可以使用以Vivado为中心的以硬件为中心的方法,在嵌入式处理器应用程序中创建预定义的硬件加速器? HLS编译器,或创建和打包优化的RTL加速器,以便作为C-库分发,从版本2016.3开始,SDAccel和SDSoC合并为一个名为SDx的软件包。 SDSoC适用于Windows和Linux。 SDAccel仅适用于某些版本的Linux。SDSoC和SDAccel的特点是FPGA项目已经逐渐消失。两个系统都允许在用C / C ++编写的原始算法级别进行建模,然后将其转换为FPGA。这允许您显着增加算法的复杂性。如果我们在VHDL / Verilog和C / C ++上比较FPGA的编程,那么它就要比较C / C ++和汇编器中传统处理器的编程。在汇编程序中,您可以制作更紧凑,更快速的代码,而在C / C ++中,您可以编写更复杂的程序。本次小编带来的是最新破解版,含安装破解图文教程,有需要的朋友不要错过了!

安装破解教程

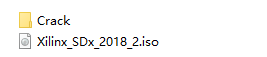

1、在本站下载并解压,得到Xilinx_SDx_2018_2.iso镜像文件和crack破解文件夹

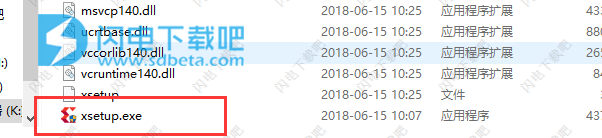

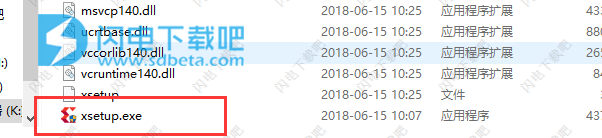

2、加载Xilinx_SDx_2018_2.iso镜像文件,如图所示,双击xsetup.exe运行安装,如图所示

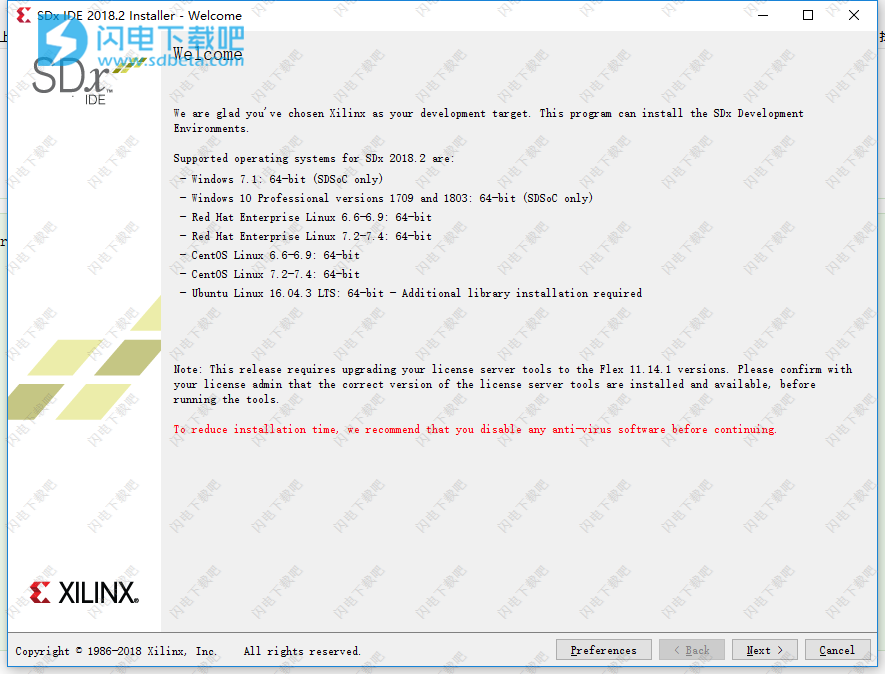

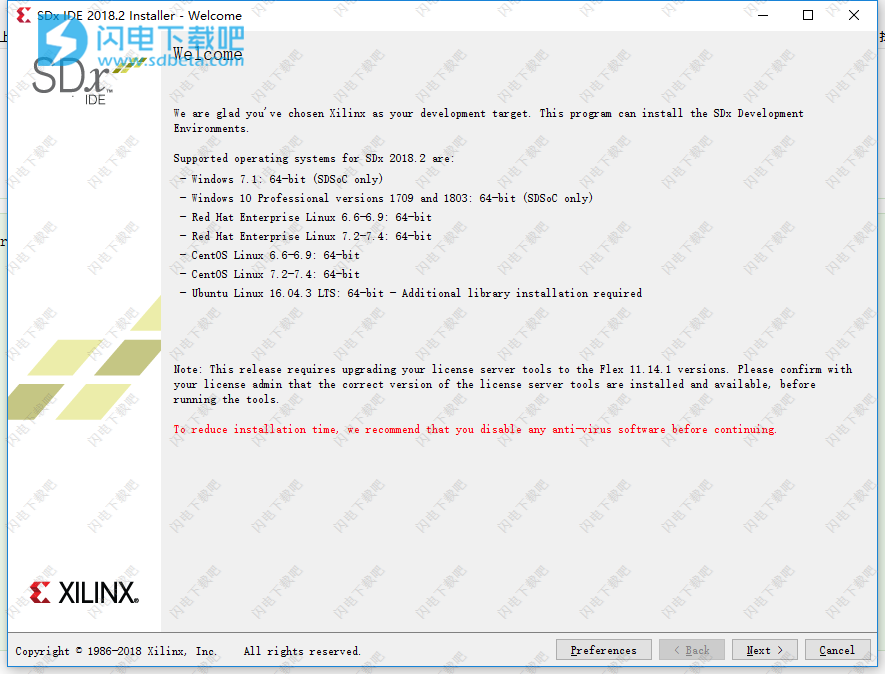

3、

我们很高兴您选择Xilinx作为您的开发目标。 该程序可以安装SDx开发环境。

支持的SDx 2018.2操作系统包括:

-Windows 7.1:64位(仅限SDSoC)

-Windows 10专业版1709和1803:64位(仅限sDSoc)

-Red Hat Enterprise Linux 6.6-6.9:64位红帽企业Linux 7.2-7.4:64位

-CentoS Linux 6.6-6.9:64位CentoS Linux 7.2-7.4:64位

-Ubuntu Linux 16.04.3 LTS:64位 - 需要额外的库安装lote:此版本需要将许可证服务器工具升级到Flex 11.14.1版本。 在运行工具之前,请与许可证管理员确认已安装并提供正确版本的许可证服务器工具。

为减少安装时间,我们建议您在继续之前禁用任何防病毒软件。点击next

4、按照提示设置安装完成

5、终于安装完成

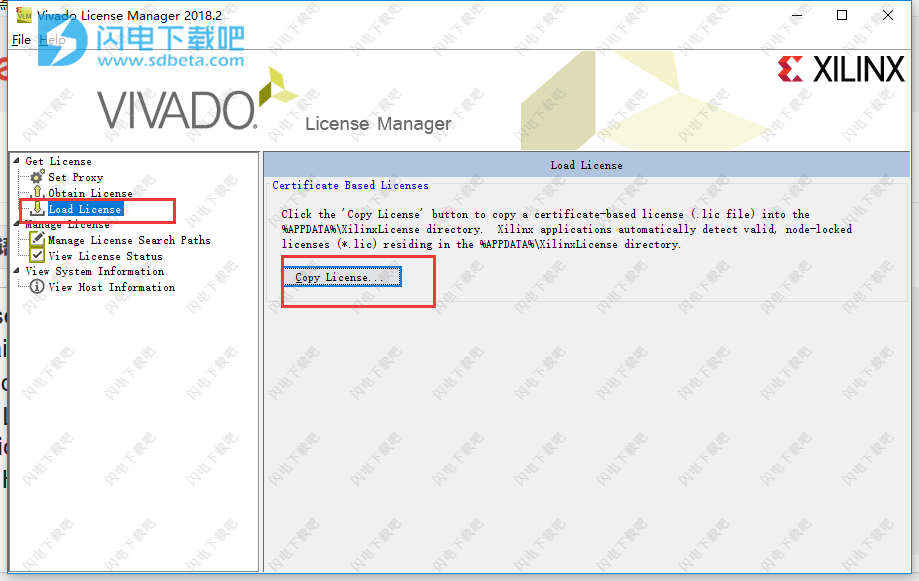

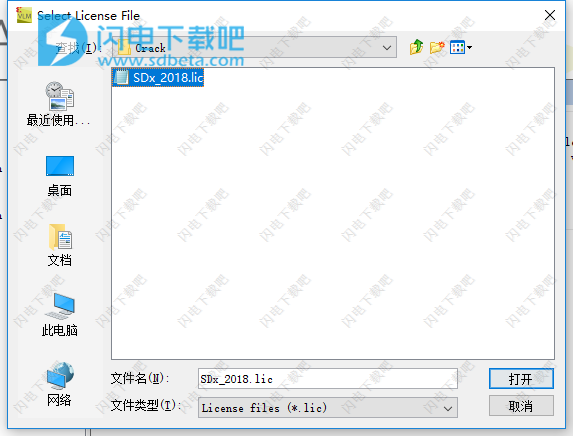

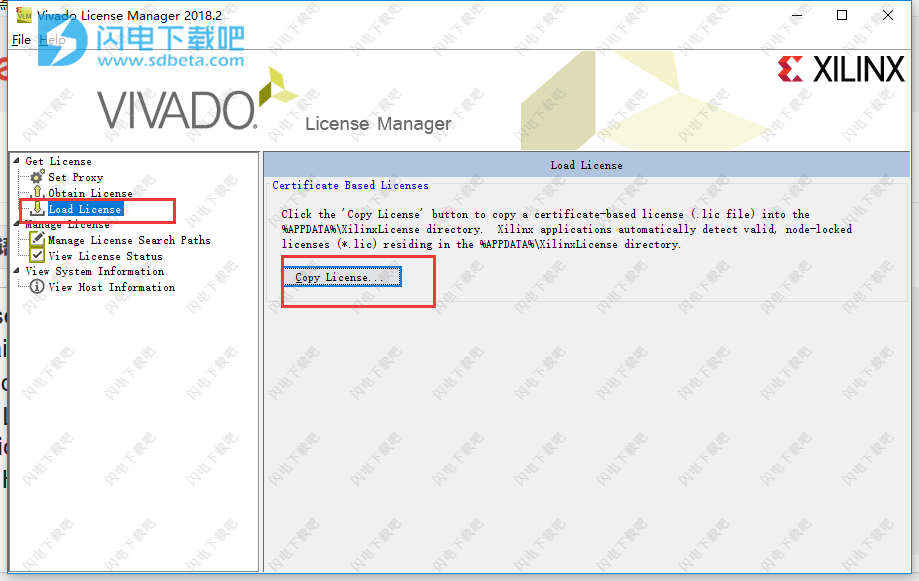

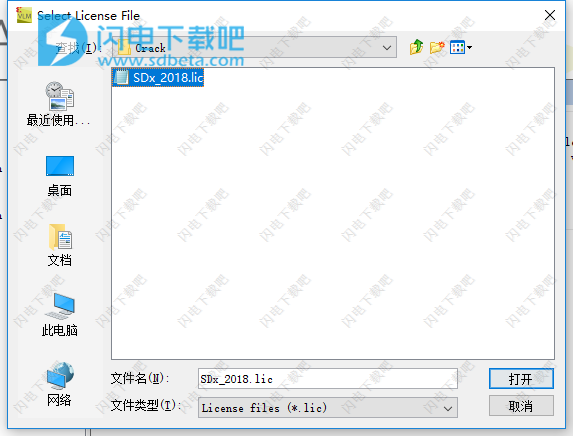

6、打开crack破解文件夹中的SDx_2018.lic

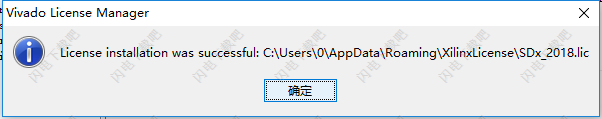

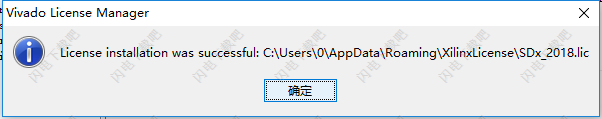

7、许可证管理器许可证安装成功:C:\ Users \ OAppData \ Roaming \ Xilinxlicense \ SDx-2018.lic

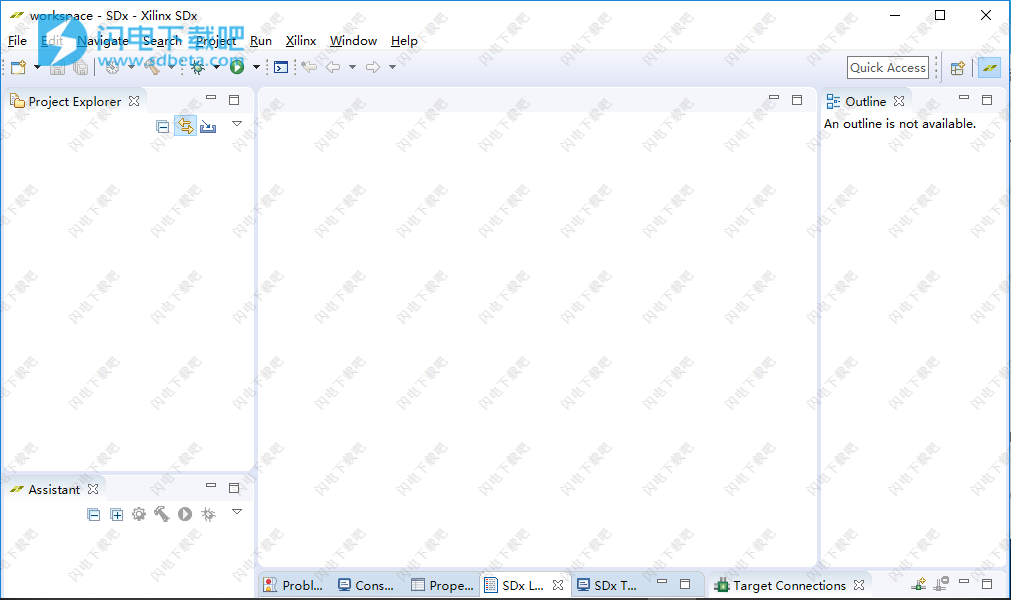

8、运行软件,

功能特色

1、基于云的加速

SDAccel™是面向基于Xilinx®FPGA的加速器板的OpenCL™应用的完整开发环境。 它可以实现系统内处理器和FPGA器件的并行编程,而无需硬件设计经验,因为整个应用程序可以用基于C语言编写。

该应用程序被捕获为用OpenCL编写的宿主程序和一组用OpenCL,C,C ++表示的计算内核。 内核仍然可以用RTL(VHDL或Verilog)编写。

Xilinx与领先的云服务提供商建立了合作关系,这些提供商专注于为大数据和机器学习提供异构加速器云,以利用C / C ++ / OpenCL的FPGA计算密度创建下一代应用。

Nimbix的产品将大大降低利用FPGA的高性能,高能效的能力来加速所有行业的高端计算工作流程的障碍。 开发人员现在可以在云中运行这些工具,然后在最新的Xilinx加速硬件上进行测试和部署,无需预先投资或购买设备。

要开始在云上进行应用程序加速,请访问http://www.nimbix.net/xilinx

2、SDSoC开发环境

熟悉SoC和MPSoC的嵌入式C / C ++ / OpenCL应用程序开发经验

熟悉的嵌入式C / C ++ / OpenCL应用程序开发经验

SDSoC™开发环境提供熟悉的嵌入式C / C ++ / OpenCL应用程序开发体验,包括易于使用的Eclipse IDE和用于异构Zynq®SoC和MPSoC部署的综合设计环境。 SDSoC具有业界首个C / C ++ / OpenCL全系统优化编译器,可提供系统级分析,可编程逻辑中的自动化软件加速,自动化系统连接生成以及加速编程的库。它还使最终用户和第三方平台开发人员能够快速定义,集成和验证系统级解决方案,并为其最终客户提供定制的编程环境。

Xilinx OpenCV库现已推出50多种硬件优化的OpenCV功能,包括Gausian,Median,Bilateral,Harris corner,Canny edge detection,HoG,SVM,LK Optical Flow等等

易于使用的Eclipse IDE可开发具有嵌入式C / C ++ / OpenCL应用程序的完整Zynq SoC和MPSoC系统

只需单击按钮即可加速可编程逻辑(PL)中的功能

支持裸机,Linux和FreeRTOS作为目标操作系统

3、系统级分析

快速的性能评估和面积估算,包括PS,数据通信和PL在几分钟内

缓存,内存和总线利用率的自动运行时检测

实现早期快速生成和探索,实现最佳的整体系统架构

4、全系统优化编译器

将C / C ++ / OpenCL应用程序编译为功能齐全的Zynq SoC和MPSoC系统

可编程逻辑中的自动功能加速,可生成ARM软件和FPGA比特流

优化系统连接,并允许快速系统探索吞吐量,延迟和区域权衡

5、平台开发人员的专家使用模型

通过成熟的方法定制定制板,将现有的Vivado项目和软件项目转换为SDSoC

基于Zynq的开发板的板级支持包(BSP)现已上市,包括ZCU102,ZC702,ZC706,以及第三方板和系统级模块(SoM),包括Zedboard,Microzed,Zybo,Avnet嵌入式视觉套件, 视频和成像套件,SDR套件等。 请单击“Board and Modules”以获取完整列表BSP。

软件优势

1、功能丰富的C/C++代码编辑器和编译环境

2、项目管理

3、应用程序构建配置和自动Makefile生成

4、错误导航

5、良好集成的环境,用于嵌入式目标的无缝调试和分析

6、源代码版本控制

7、系统级性能分析

8、专注于配置FPGA的专用工具。

9、可启动映像创建

10、Flash编程

11、可编写脚本的命令行工具

系统要求

系统要求SDAccel:

其中一个加速器的存在:

- Xilinx Kintex UltraScale KCU1500基于FPGA-E的XCKU115-FLVB2104-2的FPGA可重配置加速卡,

- Xilinx Virtex UltraScale + VCU1525是基于XCVU9P-L2FSGD2104E FPGA的FPGA可重配置加速卡。

- 具有Mat特性的加速器的主机。

-card支持PCIe Gen3 X8插槽,64GB OP,

-Disk:100 GB的可用硬盘空间。

编程计算机:

安装了环境的PC Vivado Design Suite 2018.2和Xilinx Platform Cable USB 2(HW-USB-II-G)。

操作系统红帽企业工作站/服务器7.3-7.4(64位),CentOS 7.2,Ubuntu Linux 16.04.3 LTS(64位)

SDSoC系统要求:

以下开发人员平台之一:

-ZC702,ZC706,基于Zynq-7000 SoC的ZedBoard,

-ZCU102,ZCU104,ZCU106基于Zynq UltraScale + MPSoC。

对于Windows版本:Microsoft Windows 7 / 8.x / 10 Professional(64位)

对于Linux版本:Red Hat Enterprise Workstation OS 6.7 / 6.8,Red Hat Enterprise Workstation Server / Server 7.3-7.4(64位),CentOS 7.2 / 7.3 / 7.4(64位),Ubuntu Linux 16.04.3 LTS(64-位)

使用帮助

1、使用SDSoC进行软件加速

与处理器架构相比,Xilinx中构成可编程逻辑(PL)结构的结构?设备在应用程序执行中实现高度并行性。

sdscc / sds ++(称为sds ++)为加速器中的硬件功能生成的自定义处理体系结构提供了与CPU执行不同的执行范例,并提供了显着的性能提升的机会。虽然您可以重新定位现有的嵌入式处理器应用程序以加速可编程逻辑,但编写应用程序以使用现有硬件功能库,例如修改代码以更好地使用器件架构或使用Xilinx xfOpenCV库可以显着提高性能并降低功耗。

CPU具有固定的资源,并且为任务或操作的并行化提供了有限的机会。处理器,无论其类型如何,都将程序执行为由处理器编译器工具生成的一系列指令,这些指令将用C / C ++表示的算法转换为汇编。目标处理器本机的语言结构。即使是简单的操作,例如添加两个值,也会导致必须在多个时钟周期内执行的多个汇编指令。这就是软件工程师重构算法以提高缓存命中率并减少每条指令使用的处理器周期的原因。

FPGA是一种固有的并行处理设备,能够实现可在处理器上运行的任何功能。 Xilinx SoC器件具有丰富的资源,可以对其进行编程和配置,以实现任何自定义架构,并实现几乎任何级别的并行性。与所有计算共享相同ALU的处理器不同,FPGA编程结构充当空白画布,用于定义和实现加速功能。

FPGA编译器创建了针对每种应用或算法优化的独特电路;例如,仅为神经网络实现乘法和累加硬件 - 而不是整个ALU。

sds ++系统编译器通过自动插入数据移动器和加速器控制IP,创建加速器流水线以及调用Vivado来运用FPGA架构的功能? HLS工具,它使用调度,流水线和数据流的过程:

·调度:识别数据和控制不同操作之间的依赖关系以确定每个操作何时执行的过程。编译器分析相邻操作之间的依赖关系以及跨时间和组操作,以在可能的情况下在相同的时钟周期中执行,或者在数据流依赖性允许的情况下重叠函数调用。

·流水线:一种通过重叠独立的操作或功能阶段来增加算法硬件实现中的指令级并行性的技术。

原始软件实现中的数据依赖性被保留用于功能等同,但是所需的电路被分成一系列独立的阶段。 链中的所有阶段在相同的时钟周期内并行运行。 流水线操作是一种细粒度优化,可以限制CPU限制,要求当前函数调用或操作在下一个开始之前完全完成。

·数据流:使FPGA中实现的多个功能以并行和流水线方式执行,而不是按顺序执行,实现任务级并行。 编译器通过基于输入和输出评估程序的不同功能之间的交互来提取这种并行度。

2、SDSoC应用程序的执行模型

可以根据平台启动后在目标CPU上运行的C ++程序的正常执行来理解SDSoCM应用程序的执行模型。 程序员了解C ++二进制可执行文件如何与硬件接口是很有用的。

程序中声明的硬件功能集被编译为硬件加速器,通过调用这些函数,可以使用标准C运行时访问这些硬件加速器。 每个硬件函数调用实际上都将加速器作为任务调用,并且函数的每个参数都在CPU和加速器之间传输,可由程序后加速器任务完成访问。 内存和加速器之间的数据传输是通过数据移动器完成的; 直接内存访问(DMA)引擎,由sds ++系统编译器自动插入系统,或由硬件加速器本身(如零拷贝数据移动器)插入系统。

为确保程序正确性,系统编译器拦截对硬件函数的每次调用,并将其替换为对生成的存根函数的调用,该函数具有相同的签名,但具有派生名称。存根功能协调所有数据移动和加速器操作,在硬件功能调用退出时同步软件和加速器硬件。在存根中,所有加速器和数据移动器控制都是通过sds-1ib库提供的一组发送/接收API实现的。

当硬件函数调用之间的程序数据流涉及在程序中调用函数调用之后未访问的数组参数(除析构函数或free()调用之外),并且当硬件加速器可以通过流连接时,系统编译器将通过直接硬件流连接将数据从一个硬件加速器传输到下一个硬件加速器,而不是实现往返内存的往返。此优化可以显着提高性能并减少硬件资源。

在较高级别,程序的SDSoC执行模型包括以下步骤。

1)在进入main()之前,在程序的构造函数期间初始化sds-1ib库。

2)在程序中,每次调用硬件函数都会被函数调用截获到存根函数中,该函数具有与原始函数相同的函数签名(名称除外)。

在存根功能中,会发生以下步骤:

a.将同步加速器任务控制命令发送到硬件。

b. 对于硬件函数的每个参数,异步数据传输请求被发送到适当的数据移动器,并带有相关的wait()句柄。非void返回值被视为隐式输出标量参数。

c.为每个转移请求发出屏障等待()。 如果加速器之间的数据传输是作为直接硬件流实现的,则此传输的barrier wait()发生在该参数的加速器函数链中的最后一个的stub函数中。

3)在退出main()时程序的析构函数期间发生sds -1ib库的清理。

提示:步骤2a-c确保在加速器管道的入口和出口处保留程序正确性,同时在管道内启用并发执行。

有时,程序员可以深入了解加速器任务的潜在并发执行,这些任务无法由系统编译器自动推断。在这种情况下,sds ++系统编译器支持#pragma SDS async(ID),可以在调用硬件函数之前立即插入。该pragma指示编译器生成存根函数,而不需要对数据传输进行任何屏障wait()调用。结果,在发出所有数据传输请求之后,控制返回到程序,从而在加速器运行时启用程序的并发执行。在这种情况下,程序员有责任在适当的同步点在程序中插入#pragma SDS等待(ID),这些同步点被解析为sdswait(ID)API调用以正确同步硬件加速器,它们的隐式数据移动器和中央处理器。

重要!:每个异步(ID)编译指示都需要匹配的等待(ID)编译指示。

3、SDSoC构建过程

SDSoCM环境提供标准软件开发环境的所有功能:针对嵌入式处理器应用程序和硬件功能的优化交叉编译器,可帮助您识别和解决代码中的问题的强大调试环境,性能分析器可帮助您识别瓶颈并优化您的代码。在此环境中,SDSoC构建过程使用标准编译和链接过程。

与g ++类似,sds ++系统编译器调用子进程来完成编译和链接。

如下图所示,编译不仅扩展到在CPU上运行的目标代码,还包括使用Vivado将硬件功能编译和链接到IP块中? HLS工具,并使用目标CPU工具链创建标准目标文件(.o)。系统链接包括对所有硬件功能的调用者/被调用者关系的程序分析,以及生成特定于应用程序的硬件/软件网络以实现每个硬件函数调用。 sds ++系统编译器调用所有必需的工具,包括Vivado HLS

(函数编译器),Vivado? Design Suite用于实现生成的硬件系统和Arm?编译器和链接器,用于创建在CPU上运行的应用程序二进制文件,通过输出SD卡的完整可引导系统为每个硬件功能调用加速器(存根)。

·编译过程包括以下任务:

。分析代码并运行Arm处理器上运行的主应用程序的编译,以及每个硬件加速器的单独编译。

。应用程序代码通过标准GNU Arm编译工具编译,其中一个对象(.o)文件作为最终输出生成。

。硬件加速功能是通过Vivado运行的? HLS工具,用于启动自定义硬件创建过程,以对象(.o)文件作为输出。

·编译后,链接过程包括以下任务:

。通过设计分析数据移动,并修改硬件平台以接受加速器。

。使用Vivado将硬件加速器实现到可编程逻辑(PL)区域? Design Suite用于运行综合和实现,并为设备生成比特流。

。使用硬件访问APls更新软件映像,以从嵌入式处理器应用程序调用硬件功能。

。生成集成的SD卡映像,可以使用ELF文件中的应用程序启动电路板。

4、建立目标

作为构建完整系统的替代方法,您可以创建一个包含相同平台和应用程序二进制文件的仿真模型。在此目标流程中,sds ++系统编译器将使用加速器功能的源文件创建模拟模型。 SDSoC环境提供两个不同的构建目标,用于调试和验证目的的仿真目标以及用于生成实际FPGA二进制文件的系统硬件目标:

·系统仿真:通过系统仿真,您可以在整个系统(PS / PL)中调试RTL级事务。在SDSoC仿真器(sdsoc_-emulator)上运行应用程序可让您通过调试器查看数据传输。您可以调试系统挂起,并可以在仿真波形视图中检查相关的数据传输,这使您可以查看与数据传输相关的硬件块上的信号。

·硬件:在硬件执行期间,您可以使用实际的硬件平台来运行加速的硬件功能。调试系统配置与应用程序代码的最终构建以及硬件功能之间的区别在于平台中包含特殊调试逻辑,例如系统ILA和VIO调试内核,以及用于调试目的的AXI性能监视器。

5、SDSoC开发方法

SDSoCm环境支持两个主要用例:

·以软件为中心的设计:软件程序员使用标准编程语言编写的加速应用程序的开发,将计算密集型功能加速到可编程逻辑,或通过分析应用程序来识别加速应用程序的瓶颈。

·以硬件为中心的设计:开发预定义的加速函数,用于嵌入式处理器应用程序,如内部函数库。这种设计方法可以从自上而下的方法驱动,即用C或C ++等标准编程语言编写硬件功能,然后合成为RTL,用于实现可编程逻辑;或者通过使用标准RTL设计技术来创建和优化加速功能。

这两个用例经常组合在一起,让软件和硬件开发人员团队定义硬件加速器并开发嵌入式处理器应用程序以使用它们。这种组合方法涉及应用程序的不同组件,由不同的人员开发,可能来自不同的公司。您可以使用可用于加速应用程序的库中的预定义硬件功能,例如Xilinx? xfOpenCV库,或开发您自己团队中的所有加速器。

以软件为中心的设计加速应用程序开发或加速器开发的以软件为中心的方法始于使用C或C ++编程语言。 代码编写为标准软件程序,并注意代码的特定体系结构。

以硬件为中心的设计

以硬件为中心的流程首先关注于开发和优化加速器,并且通常利用先进的FPGA设计技术来创建C-Callable IP库。 这首先是用C或C ++定义硬件功能以便在Vivado中使用? HLS,或RTL语言的使用,或Vivado中现有的IP设计或块设计? 设计套房。 硬件功能在RTL代码中定义,并合成并实现到目标设备的可编程逻辑中。在加速器应用程序中使用C-Callable IP需要软件功能签名,或者创建使用的编译函数库以供使用 跨多个应用程序。

6、使用SDSoC加速的最佳实践

在SDSoCTM环境中开发应用程序代码和硬件功能时要记住的一些具体事项:

· 一般准则:

。 通过流式传输数据而不是将数据复制到PL区域来降低资源利用率并改善并行性。 例如,在图像处理应用程序中,流构成帧的像素行而不是在一次长数据传输中复制图像帧。 重复使用PL区域的本地数据,而不是来回传输以限制DMA。

。 看看加速具有以下功能:

- 高计算时间与数据传输时间比。

- 可预测的通信流。

- 自包含控制结构 - 不需要加速器外部的控制逻辑。通过同时启动多个加速器或多个加速器实例,寻找增加任务级并行化的机会。

·对于以软件为中心的方法:

。 使用良好的内存管理技术,例如具有已知的阵列大小,并使用sds-alloc()/ sds-free()来分配/解除分配物理上连续的内存,从而减少设备占用空间并提高基准性能。

。 使用系统仿真来频繁验证您的代码,以确保它在功能上是正确的。

。 编写/迁移硬件函数以分离C / C ++文件,以便不重新编译整个设计以进行增量更改。

·对于使用C-Callable IP的以硬件为中心的方法:a跟踪AX14接口的IP或加速器的偏移量,以及哪些函数定义参数需要什么数据类型。 接口需要字节对齐。

。 维护原始的Vivado IP项目,以便快速实施对其的修改。

。 将静态库(.a)文件和相应的头文件保存在一起。

7、SDSoC环境

软件定义的片上系统(SDSoCm)环境提供了使用Xilinx实现异构嵌入式系统所需的工具? Zynq设备。 平台的概念是SDSoC环境不可或缺的一部分,它定义了硬件,软件和元数据。

构建SDSoC应用程序的数据组件。 支持Zynq器件的平台将基于Arm8的处理器系统(PS)与高性能的用户可编程逻辑相结合

(PL)开发跨硬件和软件划分系统设计的产品。

8、ilinx SDK开发流程概述

使用Xilinx®SDK为Vivado®嵌入式系统设计开发软件应用程序的典型流程如下:

调用Xilinx SDK。出现提示时,打开现有工作区或创建新工作区。

注意:创建新工作区时,请使用从Vivado®IPIntegrator生成的硬件平台。

开发您的软件应用程序Xilinx SDK提供了作为电路板支持包一部分的软件库和驱动程序的文档。

SDK为应用程序创建默认链接描述文件。链接器生成工具可用于修改内存映射。

准备好在硬件目标上测试应用程序时,通过创建运行/调试配置来运行/调试应用程序。此外,如果需要,将硬件比特流下载到FPGA器件。

您可以与软件开发并行设计硬件平台。您可以通过指向不同的版本让Xilinx SDK更新您的硬件平台规范,并让它修改新硬件平台的工作空间。

更新日志

更新了设计流程概述图。

次要文本更新。

更新的数字。

整章更新内容。

在整个章节中更新内容。

更新了PS / PL框图。

更新了流程图。

所有部分的更新。

设计流程概述图已更新为包括仿真。

章节更新。