日志:

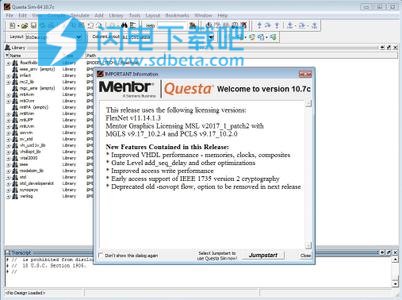

此版本中包含的新功能:

-改进的VHDL性能-存储器,时钟,合成

-门级add_seq_delay和其他优化

-改进的访问写入性能

-早期对IEEE 1735第2版加密的支持

-不建议使用的旧版-novopt流,可删除选项在下一版本的

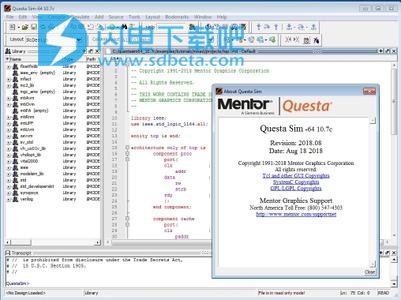

10.7c

QSIM-879中的“ 常规增强”中添加了对rtl中的位标量标量端口与SDF中“ -sdfallowvlogescapeport”下的正常非转义端口名的匹配支持。

10.7c QSIM-35477中的用户界面增强功能

-SourceDir变量改进了用于查找源文件的重新映射行为。不必定义每个源目录位置,只要定义单个根源目录就足以在目录子树中找到任何源文件,只要该子树路径与原始路径相同即可。

10.7c中的SystemVerilog增强功能

[nodvtid] -Verilog设计单元的库签名已从10.7的早期版本中更改。在10.7c中使用以前的10.7库时,需要刷新。

在10.7c中修复的用户界面缺陷

QSIM-21724-包含SV联合类型的网络或寄存器的日志记录存在多个问题,这些问题可能导致崩溃或显示不正确的数据。这些问题已经解决。

在10.7c中修复的SystemVerilog缺陷

QSIM-50272- vencrypt功能“ -auto3protect”无法正确处理模块端口列表中的宏调用语法。

QSIM-17634-(结果)与否定的时序检查一起使用时,优化的单元路径延迟可能会错误地缩短。

QSIM-8147-(结果)重新启动具有负时序检查限制的设计可能会影响仿真时序检查和功能评估行为。

在10.7c

QSIM-5497中修复了VHDL缺陷-对于某些未绑定组件中使用的类型转换的特定情况,vsim曾经崩溃。此问题已解决。

QSIM-10698-带-mixedsvvh开关的VHDL软件包不支持Verilog保留字“ global”。现在已经支持。

VISU- 4153-(结果)将VHDL记录到qwave文件时,不包括标准IEEE软件包(如stdlogic和numeric_std)的内容。现在也排除了像fixed_pkg和float_generic_pkg这样的包装。以“ float”或“ fixed”开头的标准软件包已从日志中过滤掉。

QSIM-43580-端口关联与OTHERS选项一起聚合,对于作为数组阵列的受约束端口,并且这些约束是全局静态的,则可能导致编译器内部错误或运行时有关数组长度不匹配的模拟器错误。

QSIM-26474-在某些特定情况下,在循环语句中使用切片表达式会导致崩溃。此问题已解决。

QSIM-32597-在某些特定情况下,由于某些优化,嵌套if语句的使用导致崩溃。此问题已解决。

QSIM-50516-在某些情况下,vopt会为配置生成内部错误或错误代码。如果正在配置的组件的通用端口或端口在端口/通用映射以外的任何其他地方使用,则会发生这种情况。

QSIM-50659-(结果)在某些情况下,实际值连接到过程的多个形式,则模拟输出不正确。此问题已解决。

QSIM-3588-对于for生成的某些特定情况,vsim用于崩溃。此问题已解决。

在10.7c中修复了验证管理缺陷

VM- 8783-修复了无法识别“ triage passfail”命令的“ -inputsfile”选项的错误。

版本10.6c的兼容性问题

SystemVerilog兼容性

dvt32206 - (结果)$ nochange计时检查在所有情况下都无法正常工作。

SVA / PSL兼容性

dvt101285 - (source)修正了一个错误,其中断言控制任务(例如$ assertoff)没有检查级别参数的类型并接受任何内容并将其用作整数或默认为值0.这导致了错误的行为。现在我们添加了检查,这些任务的levels参数必须是整数表达式。任何使用不正确类型指定级别的测试用例都需要修复。

验证管理兼容性

dvt101404 - (结果)通常从测试关联的UCDB合并文件中删除测试是错误的。此更改允许抑制该错误。

如何抑制:

A)从合并UCDB中删除测试

在这样的电话下:

vsim -suppress 6892 -viewcov <accumulation_mergefile> .ucdb

删除将被允许:

coverage edit -delete -test <没有覆盖的测试名称>

B)合并文件的未来累积将需要额外的抑制:

vcover merge -suppress 6891 -testassociated -out

<accumulation_mergefile> .ucdb <accumulation_mergefile> .ucdb x.ucdb

发布公告兼容性

[nodvtid] - (source,results)在正常的弃用过程之后,-novopt命令行开关将在下一个主要版本10.7中弃用:

-novopt开关将在10.7中被接受,并带有可弃用的弃用错误消息。

在10.8或后续版本中,工具将不接受-novopt开关并导致工具退出并显示错误消息。

必须更改使用此开关的客户脚本。此传统开关强制增量模式(6.0之前的行为),这是次优的,并且不再维护。

一般缺陷在10.6c修复

dvt99930 - 当子事务在父事务结束后结束时,事务记录可能会使模拟器崩溃。崩溃已得到解决。 (注意:$ transaction调用的这种顺序在技术上是不正确的;子事务应该在它们的父项之前结束。)

用户界面缺陷在10.6c中修复

dvt100029 - “when”命令有时会触发一些包含网络,矢量网和多维网络的表达式。此问题已得到解决。

dvt100318 - 允许访问命令行参数的$ argv和$ argc变量在-batch模式下不可用。此问题已得到解决。

dvt100811 - 偶尔在断言线程查看器中,分层表达式树中的文本以乱码的方式绘制。此问题已得到解决。

dvt70665 - 如果安装在包含空格的路径中,Questa和ModelSim将无法运行。此问题现已解决。

dvt101418 - 当没有给出参数时,vsim gui中的内部“ls”命令行为不正确。此命令仅在Windows上使用,此时没有找到外部“ls”命令。此问题已得到解决。

SystemVerilog缺陷在10.6c中修复

dvt32206 - (结果)$ nochange计时检查在所有情况下都无法正常工作。

dvt100404 - 在极少数情况下,涉及带有'with'子句的array.sum()约束的约束会在randomize()期间触发多维动态数组/队列的内部错误。这个问题已被解决。

dvt100885 - 在某些罕见的情况下,随机()会产生虚假(VSIM-7020)错误“非法尝试调整随机动态数组”随机与-solvefaildebug动态数组时启用。这个问题已被解决。

dvt100802 - 在SystemVerilog约束中使用DPI函数调用时,固定编译器(vopt / vlog)崩溃。

VHDL缺陷在10.6c修复

dvt101286 - 修正了一个错误,即使用命令'assertion fail -print_msg'打印的默认消息始终打印错误消息,而不管VHDL断言的严重性如何。现在,默认消息的严重性与为断言指定的严重性相同。

SystemC缺陷在10.6c中修复

dvt99466 - 而要打印的VSIM-6577错误,对于sc_module,sc_port或sc_prim_channel是在出口时被销毁全局或静态SystemC的对象,VSIM可能在一些奇怪的情况下崩溃。此问题现已修复。 vsim将报告vsim-6522警告并优雅退出。

SVA / PSL缺陷在10.6c修复

dvt101285 - (source)修正了一个错误,其中断言控制任务(例如$ assertoff)没有检查级别参数的类型并接受任何内容并将其用作整数或默认为值0.这导致了错误的行为。现在我们添加了检查,这些任务的levels参数必须是整数表达式。任何使用不正确类型指定级别的测试用例都需要修复。

验证管理缺陷修复于10.6c

dvt100091 - 如果使用“-hierarchical”命令行选项生成VRM HTML状态报告,则会发生SQL错误和格式错误。此外,非分层报告和分层报告都包含Runnable类型图标以保持一致性。

dvt101420 - 修复了VRM状态报告算法的问题,其中花费了过多的时间来维护甚至没有使用的动态状态计数器,导致状态事件日志的加载速度很慢,非常大的回归运行。

10.6c中的SystemVerilog增强功能

dvt100020 - 在'dist'运算符的RHS上添加了对'open_value_range'的支持 - 这允许指定'$'作为下限或上限的范围。

dvt100925 - 添加了对允许端口变量在-suppress 13299下声明之前使用的支持。

SVA / PSL在10.6c中的增强功能

dvt100099 - 在'assertion fail'命令中添加了一个新选项-print_msg,以便在断言失败时始终打印默认错误消息。无论操作块中指定了什么,都会打印此默认消息。如果没有操作块,则仅打印此默认消息。

10.6c中的验证管理增强功能

dvt66359 - VRM现在支持并行自动合并。通过指定“-parallelmerge <n>”激活该功能,其中<n>是单个合并文件允许的最大并发合并操作数。此外,自动合并算法将推迟使用少于5个输入UCDB的合并启动,直到最少5个UCDB排队或直到30秒通过而没有其他UCDB排队。

[nodvtid] - VRM现在支持通过修改RMDB中的某些预定义参数来修改从vrun内发送的电子邮件的mimetype和编码。

dvt101404 - (结果)通常从测试关联的UCDB合并文件中删除测试是错误的。此更改允许抑制该错误。

如何抑制:

A)从合并UCDB中删除测试

在这样的电话下:

vsim -suppress 6892 -viewcov <accumulation_mergefile> .ucdb

删除将被允许:

coverage edit -delete -test <没有覆盖的测试名称>

B)合并文件的未来累积将需要额外的抑制:

vcover merge -suppress 6891 -testassociated -out

<accumulation_mergefile> .ucdb <accumulation_mergefile> .ucdb x.ucdb

10.6c中的文档修订历史

修订 - 更改 - 状态/日期

2.3 - 改进内容的可读性和理解的修改。 Tim Peeke批准。本文档中列出了此版本中所有产品的所有技术增强,更改和修复。布莱恩拉米雷斯批准。 - 2017年7月发布

2.2 - 改进内容的可读性和理解力的修改。 Tim Peeke批准。本文档中列出了此版本中所有产品的所有技术增强,更改和修复。布莱恩拉米雷斯批准。 - 2017年5月发布

2.1 - 修改以提高内容的可读性和理解力。 Tim Peeke批准。本文档中列出了此版本中所有产品的所有技术增强,更改和修复。布莱恩拉米雷斯批准。 - 2017年4月发布

作者:内部程序和工作实践需要多位作者提供文件。在文档源中跟踪本文档中每个主题的所有关联作者。

修订历史记录:已发布的文档保留最多四次修订的修订历史记录。有关早期版本历史记录,请参阅支持中心(http://support.mentor.com)上提供的早期版本的文档。