7、通过使用UPF获得Power Aware Simulation的原生支持。

使用说明

一、模拟的基本步骤

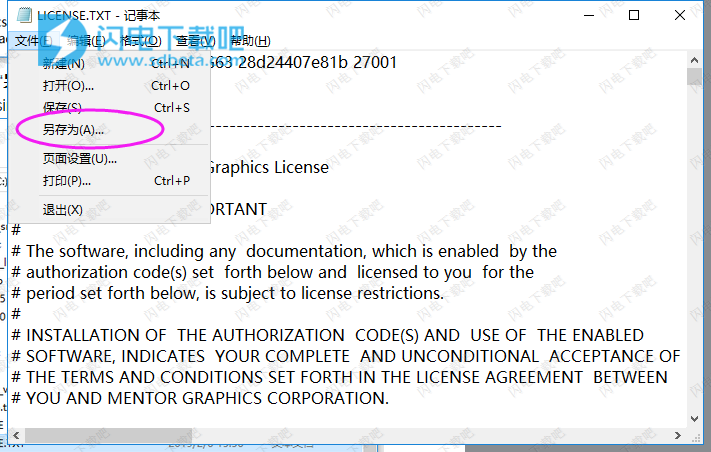

您必须拥有正确的文件和库设置才能使用QuestaSIM模拟设计所需的命令。

文件和地图库

QuestaSIM必须能够访问多种特定文件类型才能模拟您的设计。

设计文件(VHDL,Verilog和/或SystemC),包括设计的激励。

图书馆,包括工作和资源。

modelsim.ini文件(由库映射命令自动创建)。

有关QuestaSIM在系统启动期间使用的文件(包括modelsim.ini文件)的详细信息,请参阅“系统初始化”附录。

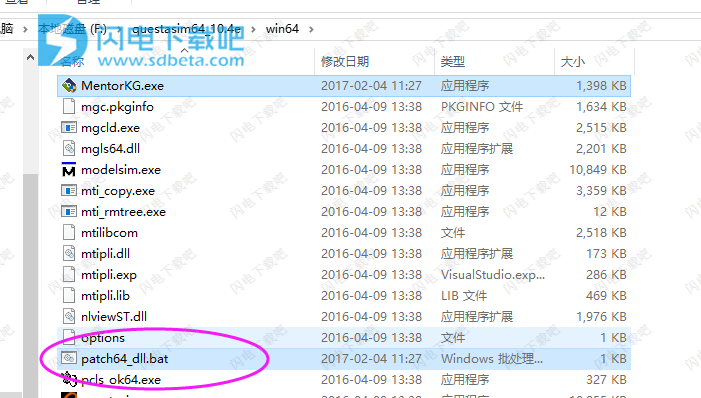

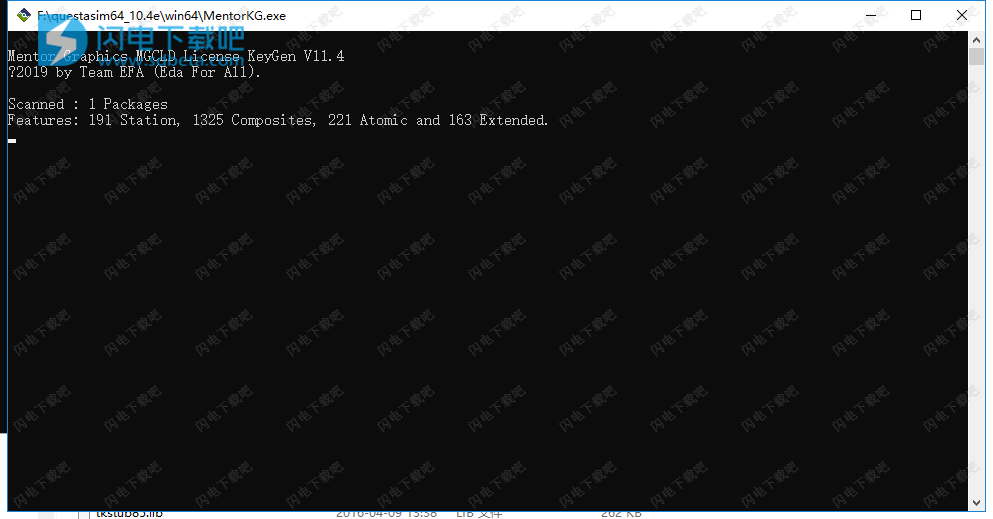

第1步-创建工作和资源库

在编译源文件之前,必须创建一个用于存储编译结果的工作库。

您可以使用vlib命令创建工作库。更新设计并重新编译时,库的内容会发生变化。

vlib命令默认创建“平面”库类型。与传统库类型相比,平面库将库信息压缩为一小组文件。这可以解决非常大的库所遇到的性能和容量问题。

由于缺少每个目标文件对象,对平面库的Makefile支持受到限制。但是,如果任何设计单元的任何源文件都比库更新,则生成的makefile将触发所有设计单元的构建。还支持平面库中的优化设计单元,具有更精确的依赖性跟踪。

执行以下任何操作时,需要vmake命令的流可以恢复为旧库类型:

在vlib命令中指定“-typedirectory”。

将modelsim.ini文件中的DefaultLibType变量设置为值0。

将shell环境变量MTI_DEFAULT_LIB_TYPE设置为值0。

对于路径包含多个需要转义的项目(例如路径名包含空格或反斜杠字符)的情况,请使用大括号({})。例如:

vmapcelllib{$LIB_INSTALL_PATH/DocumentsAndSettings/All/celllib}

先决条件

了解包含设计文件和资源库的目录的路径。

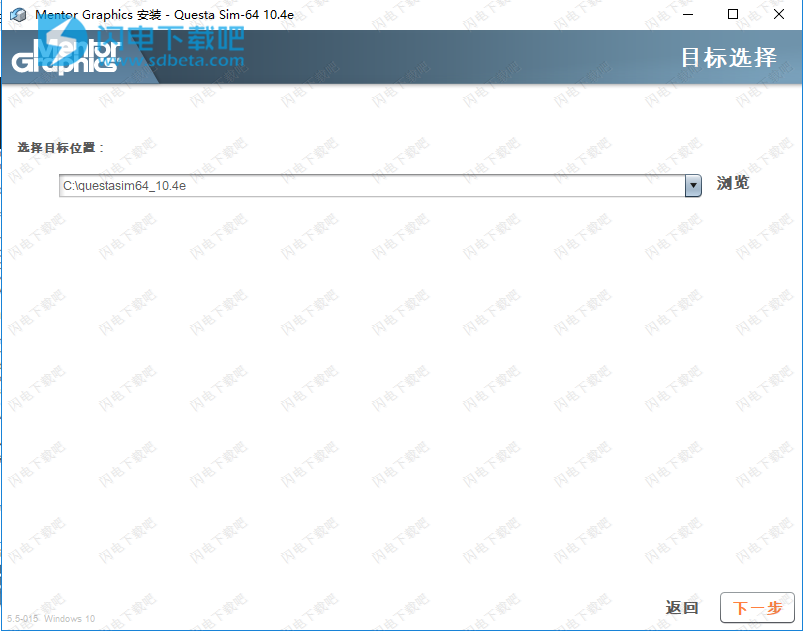

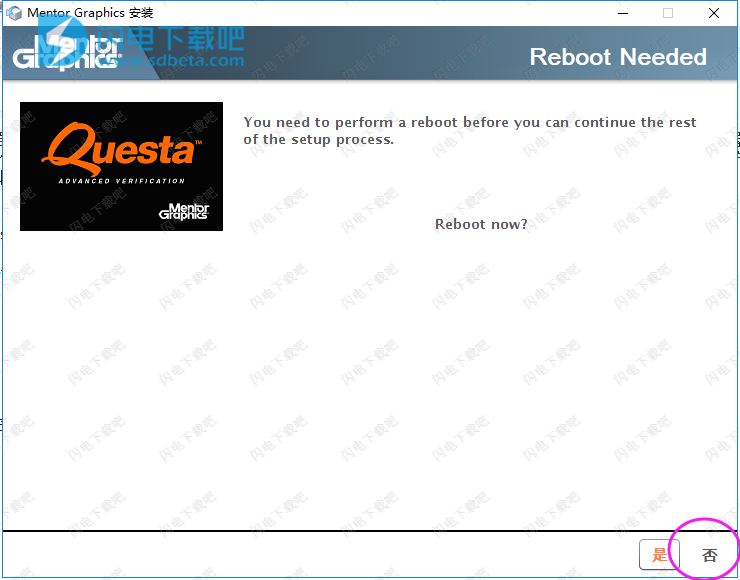

启动QuestaSIM

程序

从主菜单中选择“文件”>“更改目录”以打开“浏览文件夹”对话框。

导航到源文件所在的目录。

使用vlib命令以下列方式之一创建逻辑工作库:

在UNIXshell或Transcript窗口中输入vlib命令:

vlib的工作

从主菜单中选择“文件”>“新建”>“库”。

使用vmap命令在逻辑库名称和目录之间映射一个或多个用户提供的库:

vmap<logical_name><directory_pathname>

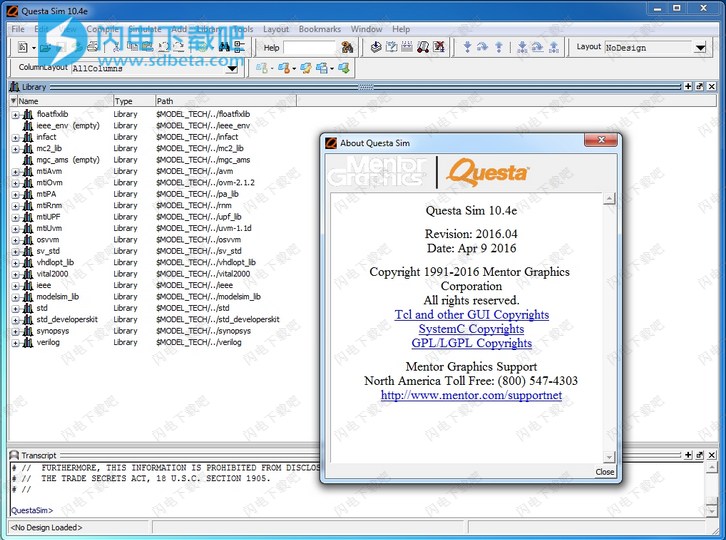

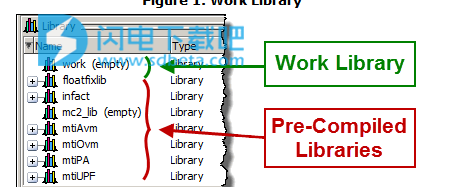

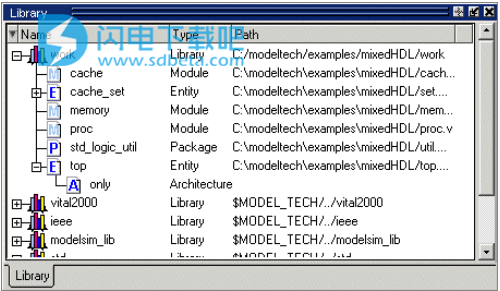

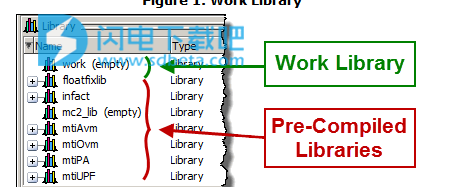

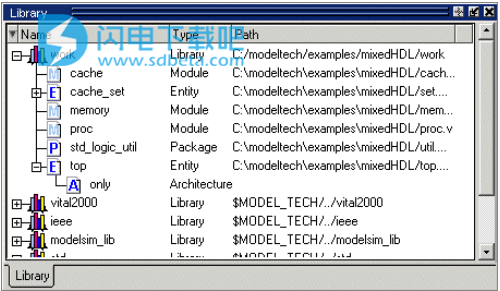

创建一个名为work的库,将其放在当前目录中,并在Structure窗口中显示工作库(图1)。

第2步-编译设计

使用特定于语言的编译器命令将设计文件编译到工作目录中。

Verilog和SystemVerilog-使用vlog命令编译。

VHDL-使用vcom命令编译。

SystemC-使用sccom命令编译。

先决条件

创建工作库并将所需的资源库映射到工作库。有关更多信息,请参阅步骤1-创建工作和资源库。

SystemC设计需要安装gcc编译器。有关更多信息,请参阅编译SystemC文件。

程序

根据用于创建设计的语言,使用以下QuestaSIM命令之一编译设计:

如果您的源文件是用...写的

在Transcript窗口中输入以下内容...

Verilog和/或SystemVerilog

您可以按任何顺序编译Verilog文件。例如:

vloggates.v和2.vcache.vmemory.v

VHDL

vcom命令按照它们在命令行中出现的顺序编译VHDL单元。对于VHDL,编译顺序很重要-您必须在引用它们的体系结构之前编译任何实体或配置。例如:

vcomv_and2.vhdutil.vhdset.vhd

SystemC的

QuestaSIM使用外部C/C++编译器将SystemC源代码编译到工作库中,而sccom-link则使用编译后的源代码并链接设计。例如:

sccom-gbasic.cpp

sccom-link

-g参数编译调试的设计。

默认情况下,编译结果存储在工作库中。(图1)

第3步-优化设计

优化是一个可选步骤,可以通过限制设计对象的可见性来提高性能。QuestaSIM使用vopt命令执行全局优化。

先决条件

创建工作库并将所需的资源库映射到工作库。有关更多信息,请参阅步骤1-创建工作和资源库。

编译设计。请参阅步骤2-编译设计。

程序

在命令行中输入以下命令:

vopttop-otopopt

哪里:

top是已编译的顶级模块的名称。

-otopopt为设计的优化版本指定名称(topopt)。

父主题:模拟的基本步骤

相关话题

使用vopt优化设计

步骤4-加载模拟设计

使用vsim命令加载设计,通过指定任何顶级模块的名称来定义(许多设计只包含一个顶级模块)。

先决条件

创建工作库并将所需的资源库映射到工作库。有关更多信息,请参阅步骤1-创建工作和资源库。

编译设计。请参阅步骤2-编译设计。

程序

在命令行中输入以下命令:

vsimtestbenchglobals

其中testbench和globals是两个顶级模块。

模拟器加载顶层模块,然后迭代加载设计层次结构中的实例化模块和UDP。这通过连接端口和解析分层引用将设计链接在一起。

注意:

通过将标准延迟格式(SDF)反标注文件应用于设计,可以将实际延迟值合并到模拟中。

第5步-模拟设计

成功加载设计后,模拟时间将设置为零,您必须输入运行命令才能开始模拟。

先决条件

对以下命令有基本的了解,通常用于运行模拟:

add wave

bp

force

run

step

使用以下任何一种方法为设计添加刺激。

基于语言的测试平台。

基于Tcl的QuestaSIM交互式命令。例如,force和bp。

VCD文件/命令。

第6步 - 调试设计

您可以从Questa SIM GUI调试您的设计。

程序

使用以下任何或所有命令开始以交互方式调试模拟:

describe

drivers

examine

force

log

checkpoint

restore

show