·符号和示意图中的图像现在可以将图像插入符号和示意图中。这可以用于创建更详细的符号,也可以用于在示意图中添加注释或文档。Windows@支持位图和矢量格式。Linux仅支持位图格式。

·AFS和EZWave集成现在,S-Edit已与AFS,EIdo和EZwave集成在一起,以在整个Linux环境中提供仿真设置,启动,交叉探测和反向标注支持。现在,使用PSF输出格式的Windows上的S-Edit和Linux上的AFS/EZWave也支持设置和启动,交叉探测和向后注释。反向注释支持包括DC OP V/l,AC小信号,模型参数,设备AC小信号参数表和设备参数反向注释。

·Layout ForgeLayout Forge是生产力提高的工具,适用于模拟布局设计人员执行设备级别的布局和布线,从而可以完全控制布局和布线。Layout Forge可以识别原理图中的差分对,放大器和电流镜,并自动在布局中生成放置和布线的单元。设计人员可以在瞬间中心的帮助下自定义设备的放置,并可以自定义工艺路线。

2019.2版本包含两个全新功能,包含在文档中,但需要调用一个键。这些是新的统一库管理器,以及称为Layout Forge的布局加速工具。如果您有兴趣使用这两种功能,请与您的销售现场应用工程师联系。他们可以代表您管理请求。

·AbutmentParameterized单元格邻接可以允许参数化单元格的实例在邻接时调整其几何形状以占据最小面积。例如,如果一个n沟道MOSFET的两个实例共享相同的源极或漏极,则基台将重新生成实例,以去除额外的触点并使这两个器件彼此非常靠近。基台将检查有效的连接,相同类型或类别的设备,并确保LVS清洁结果。必须由PDK中的铸造厂启用参数化的单元桥台。

2019.2版本包含两个全新功能,包含在文档中,但需要调用一个键。这些是新的统一库管理器,以及称为Layout Forge的布局加速工具。如果您有兴趣使用这两种功能,请与您的销售现场应用工程师联系。

库管理器工具是Tanner工具套件中的一个新应用程序。库管理器提供了一个统一的界面,用于同时在布局和示意图视图上执行操作。库管理器对库,单元和视图执行许多操作,包括:

·打开视图以在L-Edit工具和S-Edit工具中进行编辑。

软件功能

一、Tanner S-Edit原理图捕获

用户友好的原理图捕获环境,即使是最复杂的模拟/混合信号设计

Tanner S-Edit原理图捕获可在处理最复杂的IC设计时提高您的设计生产率。这种强大的环境支持在网络和设备级别进行原理图,布局和LVS报告之间的快速64位渲染和交叉探测。

行业标准支持,包括紧密的SPICE仿真集成和波形交叉探测

在原理图中直接查看工作点仿真结果

带有网络/设备突出显示的原理图,布局和LVS报告之间的交叉探测

可配置原理图电气规则检查(ERC)

先进的阵列和总线支持

与Tanner L-Edit IC集成以加快布局和ECO工艺

适用于Windows和Linux

1、易于使用

直观,易于学习的曲线可帮助您快速启动和运行

2、属性回调和每个单元格的多个视图

包括SPICE,原理图,Verilog,Verilog-A和Verilog-AMS视图

3、行业标准的进出口支持

-导出到SPICE,EDIF,Verilog和VHDL-

从OpenAccess和EDIF导入,并自动转换Mentor和其他第三方工具中的文件

二、Tanner T-Spice仿真

快速,准确,经过代工厂验证的仿真,可用于苛刻的模拟/混合信号设计

Tanner T-Spice仿真器是Tanner工具套件的一部分,可以轻松地与流程中的其他设计工具集成,并且与行业领先的标准兼容。它通过高级建模,多线程支持,设备状态绘图,实时波形查看和分析以及用于简单SPICE语法创建的命令向导,提高了仿真精度。

快速,准确的模拟/混合信号电路仿真,支持多线程

通过虚拟数据测量,参数扫描,蒙特卡洛,DC / AC和瞬态分析来准确表征电路行为

支持Levenberg-Marquardt非线性优化器,绘图语句和参数定义,以及位或总线逻辑波形输入

业内总拥有成本最低

适用于Windows或Linux

1、直观易用

快速学习曲线使您的设计师快速上手

2、铸造证明

RTL到GDSII,PDK和铸造过程支持

支持PSP,BSIM3.3和4.6,BSIM SOI 4.0,EKV 2.6,MOS 9,RPI a-SI和Poly-Si TFT,VBIC和MEXTRAM模型

3、支持关键行业标准

HSPICE和PSpice兼容的语法

Verilog-A和Verilog-AMS支持高级建模-创建任何设备的自定义模型

三、Tanner波形查看器

直观的界面,用于查看,比较和分析仿真结果

Tanner Waveform Viewer(以前称为W:Edit)提供了直观的多窗口,多图表界面,可轻松查看高度可配置格式的波形和数据。

动态链接到Tanner T-Spice仿真和Tanner S-Edit原理图捕获

直接在原理图编辑器中进行波形交叉探测

轻松处理大型(10GB +)数据文件

适用于Windows或Linux

根据其他迹线的数学表达式创建新迹线,以进行高级分析并轻松与测量数据进行比较,以最大,最小,平均,相交,均方根,均方根/过冲,幅度,误差,交叉,延迟,周期,频率,上升/下降时间,抖动,脉冲宽度,建立时间,积分,微分,占空比和压摆率

1、自动计算并显示FFT结果

dB或线性幅度

包装或未包装阶段

用于实部或虚部

2、直观易用的功能

动态注释

脚本编写

高性能跟踪导航器

3、运行时更新

在生成仿真结果时查看

四、Tanner Designer

Tanner Designer帮助团队在整个设计周期内轻松跟踪模拟验证。

Tanner Designer是一个模拟验证管理工具,可跟踪项目的所有模拟。该工具将模拟结果显示在方便的仪表板上,使团队可以快速查看哪些块通过或未通过规格并监视验证进度。该工具与S-Edit,T-Spice,Eldo和Tanner Waveform Viewer完全集成。

每次运行模拟时,Tanner Designer都会自动将测量结果发送到Microsoft®Excel®工作簿,从而使团队能够无限灵活地捕获规格要求,指定公式以计算模块是否符合规格并生成自定义报告。该团队可以立即开始管理模拟验证,而无需使用任何工具,也无需使用专有工具语言。

1、易于设置和自定义

只需指向仿真存储位置,该工具即可汇总所有测量结果

随着项目的进行逐步定制

支持多种设计验证方法

2、管理项目中的所有模拟

启动并重新运行指定的仿真

分组和排序结果

指定通过或失败参数

3、显示测量结果

将结果与参考进行比较

生成自定义报告

建立文件

五、Tanner L-Edit光子学

Tanner EDA为集成的光子学设计的设计捕获,手动实施和验证提供了完整的解决方案。

L-Edit Photonics扩展了功能齐全的布局编辑器L-Edit,以支持集成光子设计的手动布局。它使创建包含光子波导和相关电气组件的设计成为可能。设计人员可以从代工厂提供的PDK中放置光学组件,然后将它们与弯曲波导连接。设计人员可以在必要时插入交叉口。L-Edit Photonics可以将波导精确地卡接到光学引脚上,以确保波导与设备的完美连接。

L-Edit Photonics支持以布局为中心的设计流程,该流程不需要原理图。这种方法的好处是布局是“黄金”设计数据库,想要使用原理图的设计人员可以使用S-Edit。

该工具生成一个网表,用作光子模拟器的输入。

L-Edit Photonics与仿真厂商合作。我们的合作伙伴包括Luceda,Lumerical,Optiwave和VPIphotonics™。

可以从同时支持Tanner L-Edit Photonics和LightSuite Photonic Compiler的多家铸造厂处购买光子PDK。该工具支持iPDK和Mentor格式的PDK。

L-Edit Photonics在Linux®和Windows®上均可用。

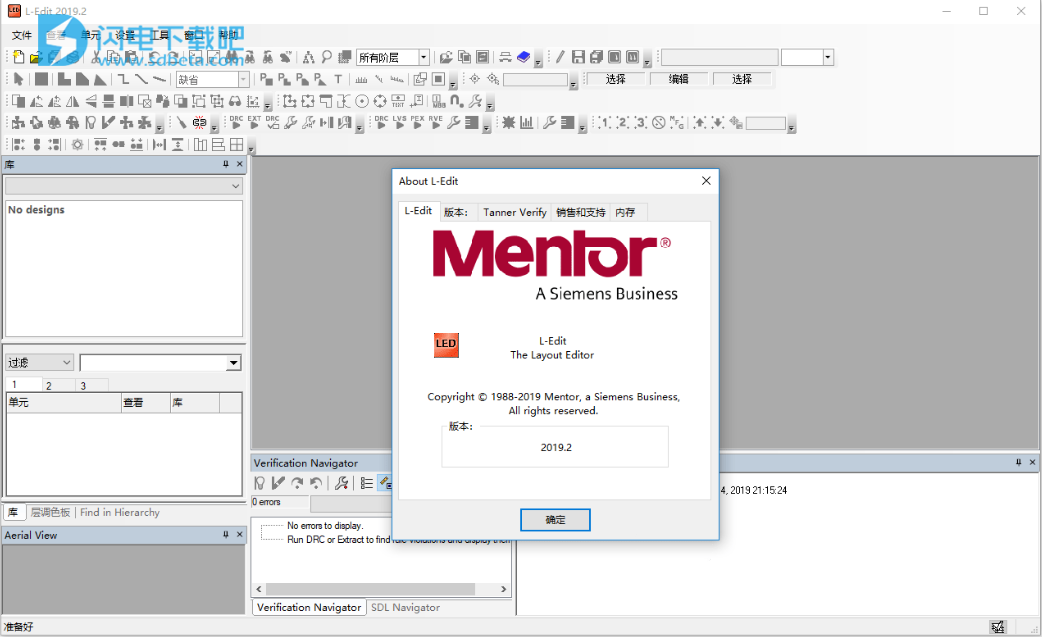

六、Tanner L-Edit IC布局

灵活且高度可配置的完整模拟/混合信号IC物理设计环境

创建与原理图首次匹配的布局,以最大化效率并减轻CAD经理的支持负担。通过平台独立性和灵活的许可轻松启动和运行。减少手动路由:

实时净飞线

网和别针追踪

几何标记/突出显示/通过网络

生态追踪

适用于Windows和Linux

1、完整的分层物理布局

丰富的环境,具有许多易于使用的功能,包括:

对象捕捉

节点突出显示

宏支持

布局生成器

2、支持关键的行业标准

OpenAccess读/写

示意图驱动布局(SDL)支持

使用T-Spice HSPICE,PSpice,结构性Verilog或CDL格式的网表文件

3、优化性能

快速渲染速度和交互式实时设计规则检查(DRC)

4、广泛的工具选项和附加组件

利用专用工具和模块(包括Tanner SDL路由器)扩展Tanner L-Edit IC功能。

5、直接口径® /口径RVE支持,EVI

Tanner外部验证接口(EVI)与Caliber工具套件无缝集成,使您可以利用两种环境的投资

七、坦纳数字实施者

集成的,灵活的数字综合和布局布线工具,可加快模拟/混合信号设计的开发

由Oasys综合和Nitro布局和路线引擎提供支持的Tanner数字实现器(TDI)已集成到Tanner的物理布局工具L-Edit中,以解决“顶部模拟”设计数字需求的物理实现。越来越多的模拟设计正变得数字化,从而产生更多的数字内容来增强模拟功能,例如自动校准和更多的可编程性。

L-Edit中的Tanner Digital Implementer集成是理想的经济高效,易于使用的数字综合和布局布线解决方案。

时间驱动的位置和路线

支持低功耗设计方法

平面图和电源计划功能

1、直观,快速的学习曲线,可进行综合和布局布线

Tanner的物理布局工具L-Edit与Tanner Digital Implementer完全集成,因此非常适合结合模拟和数字的IoT设计。

2、导入设计数据,技术数据并指定时间

利用简化的用户界面,通过导入技术数据用户(例如LEF,Liberty和PTF文件)快速放置和路由ADC的控制块,通过指定时钟或通过SDC文件来指定要使用的Verilog网表并定义时序要求。

3、定义平面图和电源计划要求

对于平面图需求,您可以指定芯片尺寸,边距和行站点名称,或者在布局中或通过DEF平面图文件定义需求。设置电源需求时,可以指定电源/ gnd环形和条纹参数,或者在布局中或通过DEF平面图文件定义需求。设置完成后,您可以在L-Edit中执行放置和布线查看结果。

八、TannerCalibre®One DRC / LVS / xRC

使用Calibre行业领先的DRC,LVS和寄生提取工具,可以自信地完成模拟/混合信号设计。

该坦纳口径一个IC验证套件是坦纳™模拟/混合信号(AMS),物理设计环境的一个组成部分,创造了一条捷径口径验证工具的验证能力。

Tanner-Calibre One是Tanner完整的全流模拟/混合信号(AMS)IC设计套件的关键部分。

Tanner原理图捕获工具S-Edit和物理布局编辑器L-Edit与Calibre验证套件紧密集成。

Caliber平台是物理验证的行业领导者,并已获得每个主要IC代工厂的签核资格,并且Tanner Calibre One验证套件使用相同的Calibre设计套件。

Tanner机芯一个DRC / LVS / xRC许可证只能与Tanner L-Edit一起使用。

1、口径nmDRC

分层设计规则检查

口径nmDRC™确保可以制造物理布局。这个行业领先的工具提供了快速的周期时间和创新的设计规则功能。

2、机芯xRC

寄生提取

Calibre xRC™验证了与布局有关的影响不会对设计的电气性能产生不利影响,可提供准确的寄生数据,以进行全面,准确的布局后分析和仿真。

3、口径nmLVS

分层布局与示意图

口径nmLVS™会检查物理布局在电气和拓扑上是否与原理图相同。它通过提供实际的器件几何尺寸测量和先进的交互式调试功能来确保准确的验证,从而提高了设计人员的生产率。

4、口径RVE

图形结果查看环境

Caliber RVE™将解决方案整合在一起,提供了一个图形化的结果查看环境,可通过立即直观地识别设计问题并在L-Edit和S-Edit中交叉选择相关问题来减少调试时间。

5、机芯互动

Calibre Interactive:Calibre®Interactive™是用于Caliber DRC™,LVS和xRC™工具的调用GUI,用于物理验证和寄生提取。它与L-Edit布局设计环境紧密集成。

九、Tanner Eldo RF

将混合信号仿真扩展到RF域,TannerEldo®RF通过采用一组专用算法来准确,有效地处理这些应用中的低功率信号,为连接的传感器和物联网市场中的无线应用提供了可靠的RF验证。

Tanner Eldo RF扩展了Eldo仿真器的功能,以提供广泛的分析功能,一组RF专用功能以及适用于各种电路类型的一组强大的优化功能。

1、特点和优点

用于无线应用的全芯片RF IC验证

无缝集成到Mentor Graphics和其他领先的IC设计流程中

PLL和频率合成器的闭环相位噪声分析

包含数千个元素的大型RF IC设计的多音稳态分析

射频/基带划分的调制稳态分析

适用于所有无线标准的数字调制源库

强非线性信号分析

内置优化功能

2、射频分析功能

稳态,稳态小信号和稳态噪声

调制稳态

振荡器和相位噪声

分频器

数字调制源

参数扫描

锁相环

Tanner Eldo RF集成了强大的优化算法,可帮助设计人员对电路性能进行微调。优化工具不需要任何外部工具,因为它们都集成在仿真内核中,以实现最大效率。它支持连续和离散,受约束或不受约束的参数,并同时优化多个模拟和分析。

Tanner EZwave™波形工具提供了对RF,低频基带模拟和数字信号进行操作所需的高级功能。它可以在频域和时域中处理数据。史密斯圆图,眼图,带有复杂窗口的FFT或信噪比计算只是其中的一些内置功能。

与Tanner IC设计套件的深度集成包括以下功能:

直接从S-Edit原理图捕获工具运行Tanner Eldo RF

直接在原理图上显示工作点结果

在Simulation Setup用户界面中直接指定用于RF分析的仿真模式

交叉探针波形