Questa SIM 2020破解版是用于VHDL,Verilog,SystemVerilog,SystemC和混合语言设计的验证和仿真工具。包括设计优化、基本模拟流程、项目流程、多个库流、调试工具等多方面功能和优势!默认情况下,Questa SIM优化会在所有设计上自动执行。这些优化旨在最大程度地提高模拟器性能,在某些Verilog设计中,与未优化的运行相比,最多可提高10倍。但是,全局优化可能会影响您可以查看的设计仿真结果的可见性-某些信号和过程可能不可见。如果这些信号和过程对于调试设计很重要,则可能有必要通过从特定模块中删除优化来定制仿真。因此,重要的是要就如何最好地将优化应用于您的设计做出明智的决定。在Questa SIM中执行全局优化的工具称为vopt。在Questa SIM中模拟设计基本步骤包括创建工作库、编译设计、在设计中加载模拟器并运行模拟、调试结果。如果未获得预期的结果,则可以使用Questa SIM调试环境来跟踪问题的原因。有需要的朋友不要错过了!

安装激活教程

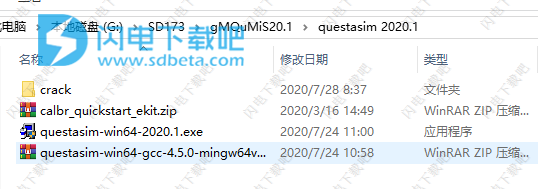

1、在本站下载并解压,如图所示

2、运行questasim-win64-2020.1.exe开始进行安装,选择软件安装位置

3、点击同意

4、安装完成,退出向导

5、在C盘根目录中创建一个flexlm文件夹。然后打开安装包中的crack文件夹,把crack1中的MentorKG.exe和patch64_dll.bat拷贝到C:\questasim64_2020.1\win64下。

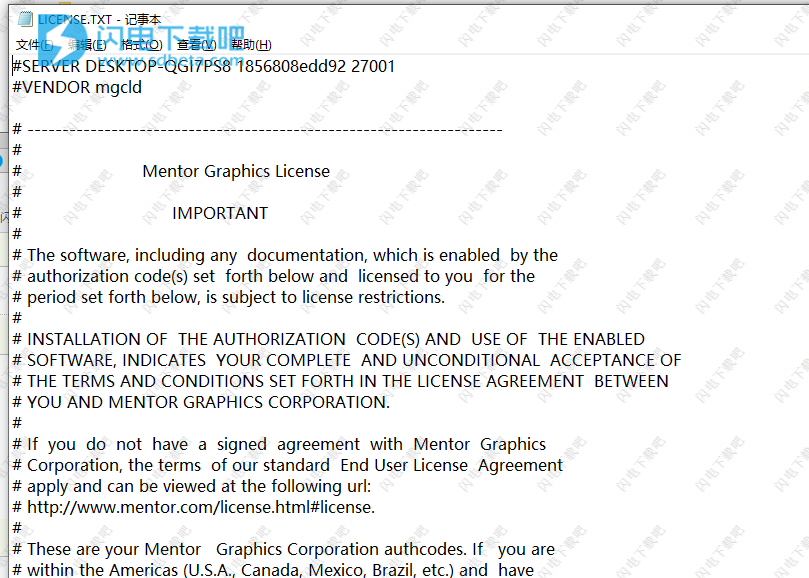

6、运行patch64_dll.bat,等待并生成一个LICENSE.TXT文件,将它保存到C:\flexlm\LICENSE.TXT中

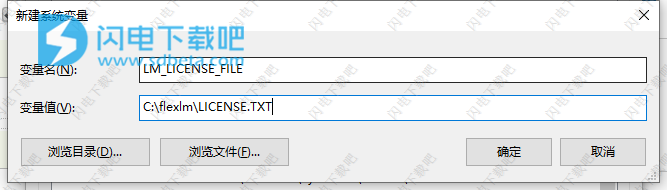

7、创建系统环境变量,

变量名:LM_LICENSE_FILE

变量值:C:\flexlm\LICENSE.TXT

8、完成后,打开安装包中,把win64文件夹中的mgcld64.exe和mgls64.dll文件复制到默认C:\questasim64_2020.1\win64中,点击替换目标中的文件

9、运行程序,可以正常打开,破解完成。

注意:新版本的程序已经不能使用-novopt选项vsim命令,把-novopt更换为-voptargs=+acc即可,不会出现信号被优化掉不能显示的情况。

软件功能

1、适用于最复杂的回归套件的高性能多语言引擎

2、高效的高级验证解决方案,具有验证管理功能,可覆盖大型复杂电子系统的覆盖范围

3、通过本机断言和完整的多抽象和多语言调试环境(包括事务级调试),易于使用,快速调试

4、约束随机刺激生成以自动化测试开发

5、具有OVM和UVM的本机高级SystemVerilog测试平台功能与独特的调试功能相结合,可简化高级测试平台的开发和调试

6、高带宽事务级(TBX)与Veloce平台的集成,可实现显着的仿真加速

7、使用UPF对Power Aware Simulation进行原生支持

8、多核仿真,支持所有设计语言和构造,并自动或手动分区设计以并行运行,同时维护单个数据库以进行调试和覆盖。

软件特色

1、将高性能和容量仿真与高级调试和功能覆盖功能相结合,为Verilog,VHDL,SystemC和UPF等提供全面的本机支持。

2、通过非常积极的全球编译以及VHDL和SystemVerilog的仿真优化算法,实现了行业和容量的领先性能。

3、提供全面的,基于标准的ABV解决方案,从而提供SystemVerilog和属性规范语言的选择。

4、获得了Questa验证库(QVL),这是一个完整的SystemVerilog断言检查器和监视库,可以很容易地采用ABV。

5、配备高性能,多语言引擎,适用于大多数复杂的回归套件。

6、与Veloce平台进行高带宽事务级集成,以实现显着的模拟加速。

7、通过使用UPF获得Power Aware Simulation的原生支持。

使用帮助

一、创建工作设计库

在模拟设计之前,必须首先创建一个库并将源代码编译到该库中。

程序

创建一个新目录,并将本课程的设计文件复制到其中。

首先为该练习创建一个新目录(以防其他用户使用这些课程)。

Verilog:将counter.v和tcounter.v文件从/<install_dir>/examples/tutorials/verilog/basicSimulation复制到新目录。

VHDL:将counter.vhd和tcounter.vhd文件从/<install_dir>/examples/tutorials/vhdl/basicSimulation复制到新目录。

如有必要,启动Questa SIM。

在UNIX Shell提示符下键入vsim或在Windows中使用Questa SIM图标。

首次打开Questa SIM后,您将看到“欢迎使用Questa SIM”对话框。单击关闭。

选择文件>更改目录,然后更改为您在步骤1中创建的目录。

创建工作库。

选择文件>新建>库。

这将打开一个对话框,您可以在其中指定库的物理名称和逻辑名称(图1)。您可以创建新库或映射到现有库。我们将做前者。

图1.创建一个新库对话框

在库名称字段中输入work(如果尚未自动输入)。

单击确定。

Questa SIM创建一个名为work的目录,并将一个名为_info的特殊格式的文件写入该目录。_info文件必须保留在目录中,以将其区分为Questa SIM库。不要从操作系统中编辑文件夹内容;所有更改都应在Questa SIM中进行。

Questa SIM还将库添加到“库”窗口(图2),并在Questa SIM初始化文件(modelsim.ini)中记录库映射以供将来参考。

图2.工作库添加到“库”窗口

当您在上面的步骤3c中按确定时,以下内容被打印到“成绩单”窗口中:

vlib工作

vmap工作

这两行是您所做菜单选择的等效命令行。许多等效的命令行将以这种方式回显其菜单驱动的功能。

二、编译设计单元

创建工作库后,就可以编译源文件了。

您可以使用图形界面的菜单和对话框来编译源文件,如下面的Verilog示例所示,或者在Questa SIM>提示符下输入命令。

程序

编译counter.v和tcounter.v。

选择编译>编译。这将打开“编译源文件”对话框(图1)。

如果“编译”菜单选项不可用,则可能已打开一个项目。如果是这样,请通过激活“库”窗口并从菜单中选择“文件”>“关闭”来关闭项目。

从“编译源文件”对话框中选择counter.v和tcounter.v模块,然后单击“编译”。这些文件被编译到工作库中。

编译完成后,单击“完成”。

图1.编译源文件对话框

查看编译的设计单位。

在“库”窗口中,单击工作库旁边的“+”图标,您将看到两个设计单元(图2)。您还可以查看其类型(模块,实体等)以及基础源文件的路径。

图2.编译到工作库中的Verilog模块