Synopsys Synplify P-2019破解版是领先的综合软件工具,使用旨在为用户提供领先的工具以提高省内颤栗,减少运行时间,减少错误风险!提供先进的综合算法,提高运行速度,该工具是生产高性能和高性价比FPGA设计的行业标准。Synopsys FPGA设计工具由综合和调试工具组成,使设计人员能够以最低的进度风险将具有竞争力的产品快速投放市场。Synplify综合工具提供了快速的运行时间,性能,用于成本和功耗降低的区域优化,多FPGA供应商支持,增量和团队设计功能,以加快FPGA设计开发的速度。此外,Synplify支持DesignWare IP集成,与VCS高性能功能验证的链接,与Identify RTL Debugger的集成以及与ASIC兼容的综合流程。提供了快速的硬件交付时间,具有深度的调试可见性,增量设计,广泛的语言支持以及基于FPGA的产品的最佳性能和区域。全新2019破解版下载,有需要的朋友不要错过了!

安装激活教程

1、在本站下载并解压,首先,确保您的计算机仅通过网卡(最好是以太网)连接到Internet,并且已禁用防病毒功能。

2、运行fpga安装文件fpga_vP-2019.03-SP1_win.exe开始安装程序,如图所示,输入13131作为站点ID,输入1212312312作为联系信息

3、勾选我接受 许可证协议条款

4、选择软件安装路径,将程序安装在默认位置。

5、安装完成,退出向导,转到Crack文件夹,在以管理员身份运行模式下运行SCL_v2018安装文件,不要更改显示的值,只需单击下一步,最后完成

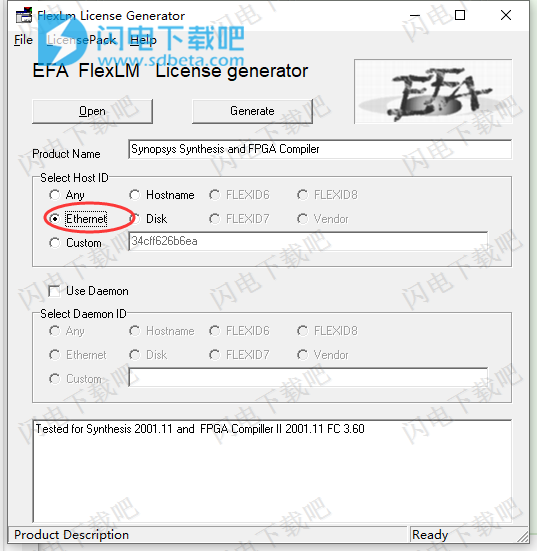

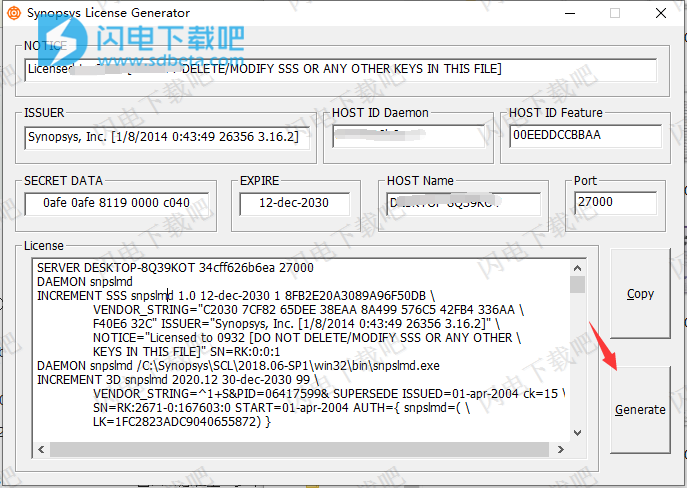

6、运行LicGen.exe文件,单击“open”,然后选择并打开显示的Synopsys.lpd文件

7、从“选择主机ID”部分中选择“以太网”选项,先放着不管,不要关闭

8、打开文件夹C:\ synopsys \ SCL \ 2018.06-SP1 \ win32 \ bin(安装的SCL版本可能不同,只需转到C:\ synopsys \ SCL并根据您的版本继续其余的操作),按住Shift键并右键单击snpslmd.exe文件,然后选择“复制为路径”。

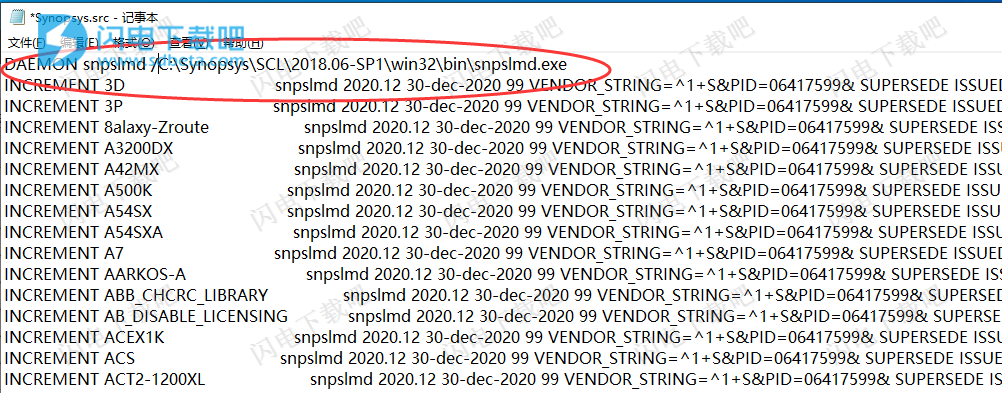

9、再次转到Crack文件夹,使用记事本打开Synopsys.src文件,删除第一行开头的#符号,然后选择短语home / EDA / Synopsys / scl_v2018.06 / linux64 / bin / snpslmd /右键单击并粘贴,同时删除短语开头和结尾的两个“”符号(第一行应如下所示:DAEMON snpslmd C:\synopsys\SCL\2018.06-SP1\win32\bin\snpslmd.exe )

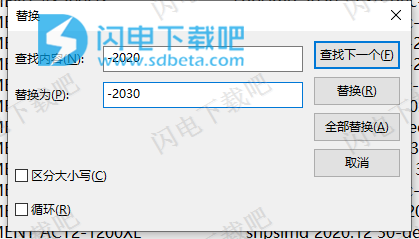

10、从“编辑”菜单中,选择“替换”,在“查找内容”字段中输入短语-2020,在“替换为”字段中输入-2030,然后单击“全部替换”(检查文件中的日期是否更改为30-dec-2030)。保存并关闭文件。

11、运行scl_keygen.exe文件,在NOTICE(通知)部分中输入您的用户名,而不是Student @ eetop,在EXPIRE(输入)部分中,将日期更改为2030-dec-2030,然后在HOST Name(主机名称)部分中,输入以下内容的全名:你的电脑。 (要找到此名称,您可以转到此PC,右键单击空白处,然后单击“属性”)

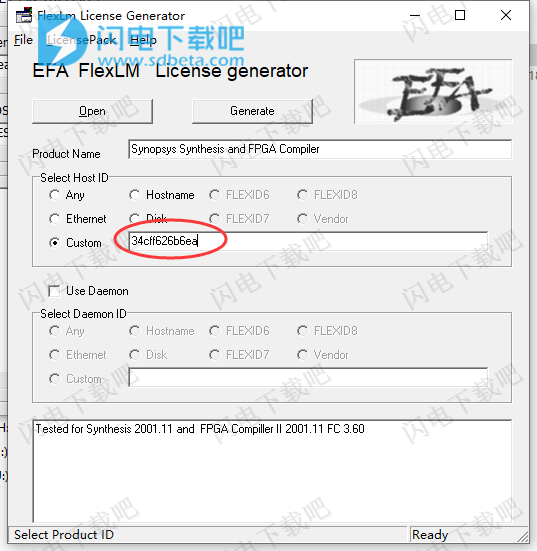

12、在FlexLm License Generator窗口中,在Select Host ID部分中,选择自定义选项,然后选择并复制其前面显示的短语并关闭此窗口,然后返回Synopsys License Generator。窗口(您在上一步中打开的窗口)并将复制的短语替换为HOST ID Daemon

13、单击“generate”,然后等待文本显示在“license”部分中,然后关闭此窗口。

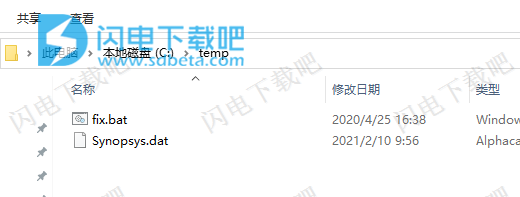

14、在驱动器C的根目录中创建一个名为temp的文件夹,然后从crack文件夹中复制Synopsys.dat和fix.bat文件,并将这些文件复制到创建的文件夹中

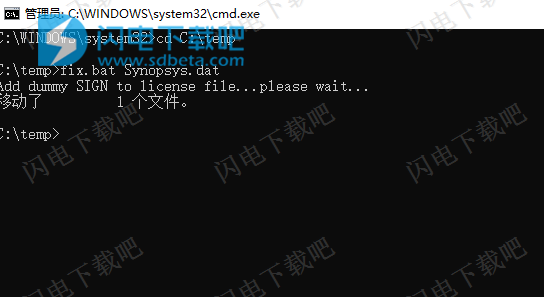

15、在“以管理员身份运行”模式下运行CMD,输入命令cd C:\temp,点击enter,然后输入命令fix.bat Synopsys.dat,点击enter并等待作业完成并关闭CMD

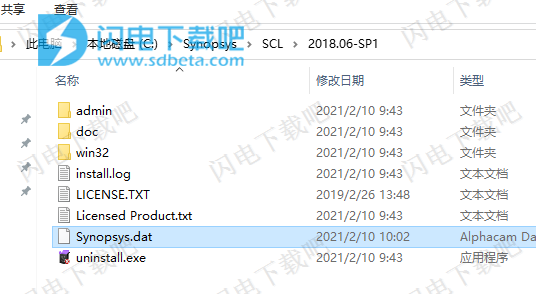

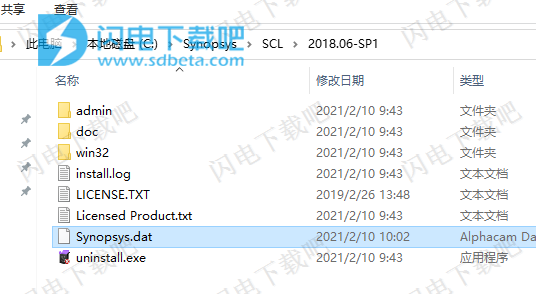

16、从temp文件夹复制Synopsys.dat文件,然后将其复制到C:\Synopsys\SCL\2018.06-SP1

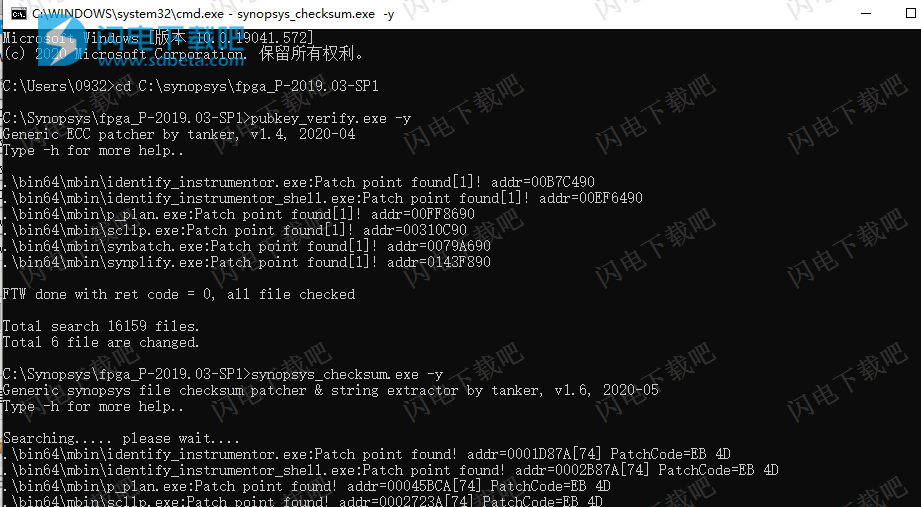

17、再次转到Crack文件夹,复制4个文件pubkey_verify,pubkey_verify.exe,synopsys_checksum,synopsys_checksum.exe,并分别将它们粘贴到以下目录中:

C:\ synopsys \ SCL \ 2018.06-SP1

C:\ synopsys \ fpga_P-2019.03-SP1

18、在“以管理员身份运行”模式下再次运行CMD,输入命令cd C:\synopsys\fpga_P-2019.03-SP1,然后按Enter,然后运行两个命令pubkey_verify.exe -y和synopsys_checksum.exe -y,然后等待工作完成。然后输入命令cd C:\synopsys\SCL\2018.06-SP1并点击enter,然后再次分别输入两个命令pubkey_verify.exe -y和synopsys_checksum.exe -y,然后enter并等待要做的工作。关闭CMD

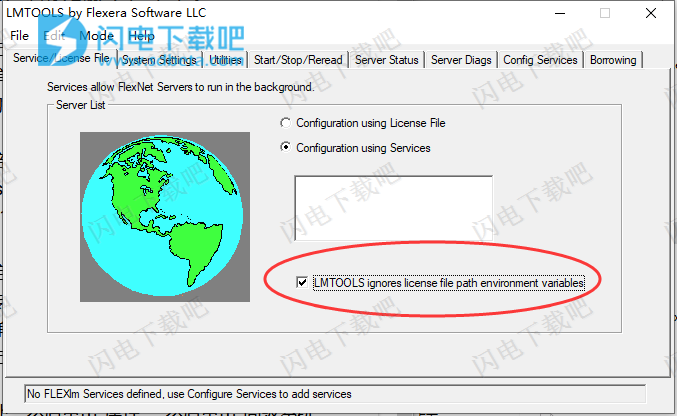

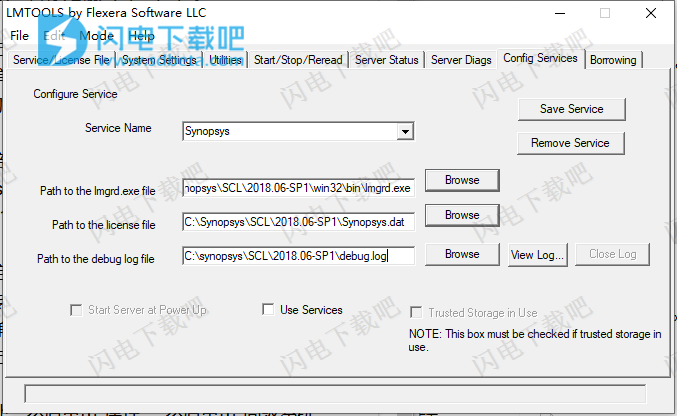

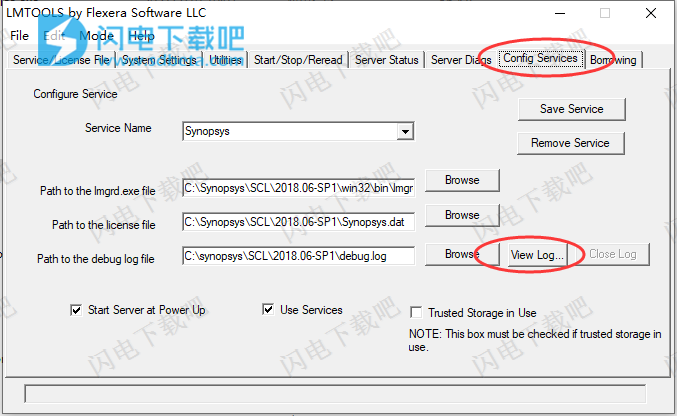

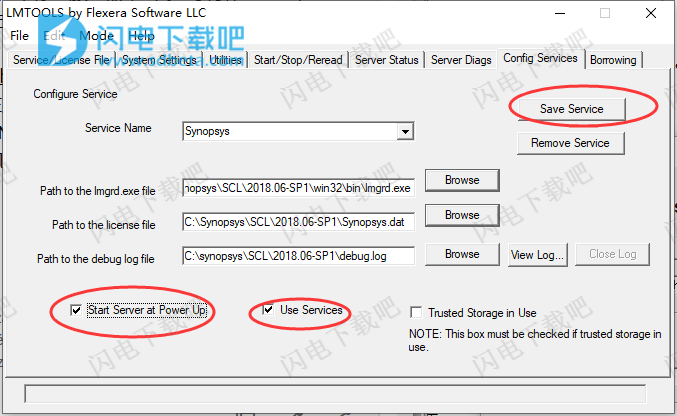

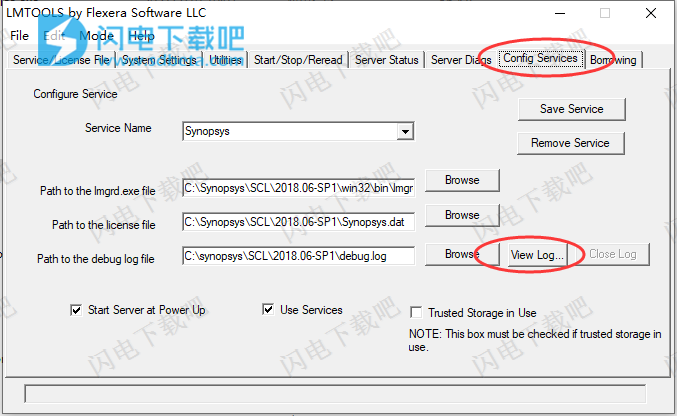

19、转到C:\ synopsys \ SCL \ 2018.06-SP1 \ win32 \ bin并打开lmtools.exe。检查“ LMTOOLS忽略许可证文件路径环境变量”选项,转到“配置服务”选项卡,然后在服务名称处输入Synopsys。

20、在lmgrd的路径部分中,单击浏览选项,然后选择lmgrd.exe文件。在许可证文件的路径部分中,单击浏览选项,转到C:\ synopsys \ SCL \ 2018.06-SP1,在窗口的右下角单击“许可证文件(* .Lic)”,然后单击许可证文件(* .Dat),然后选择并打开出现的Synopsys.dat文件。在``调试日志文件的路径''部分中,替换为C:\synopsys\SCL\2018.06-SP1\debug.log

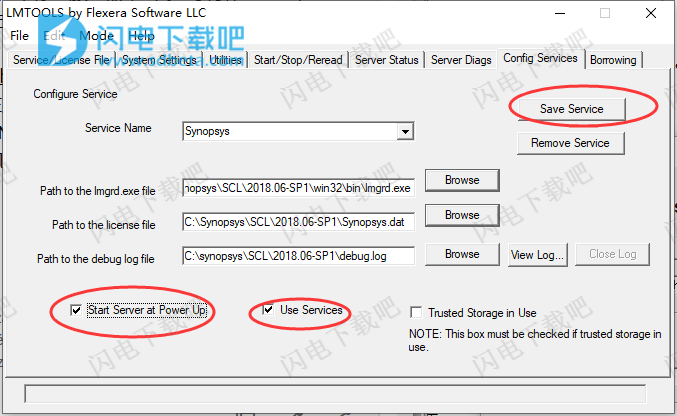

21、选中“使用服务并在启动时启动服务器”选项,然后单击“保存服务”(然后单击“是”和“确定”)

22、转到“启动/停止/重新读取”选项卡,选中“force server shutdown”选项,然后单击“stop server”。等待作业完成,然后单击start server,然后单击“ReRead License File”

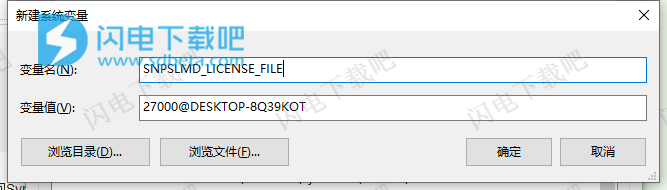

23、转到此PC,右键单击空白处,然后单击“属性”,然后单击“高级系统设置”,再单击“环境变量”。在用户变量和系统变量中,单击“新建”,在名称位置输入SNPSLMD_LICENSE_FILE,在值位置输入27000@你的电脑名称

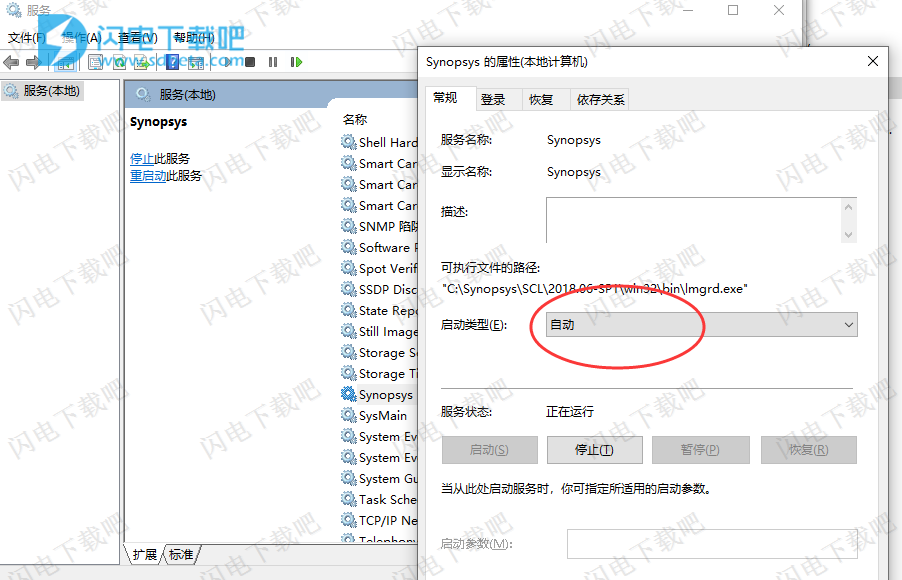

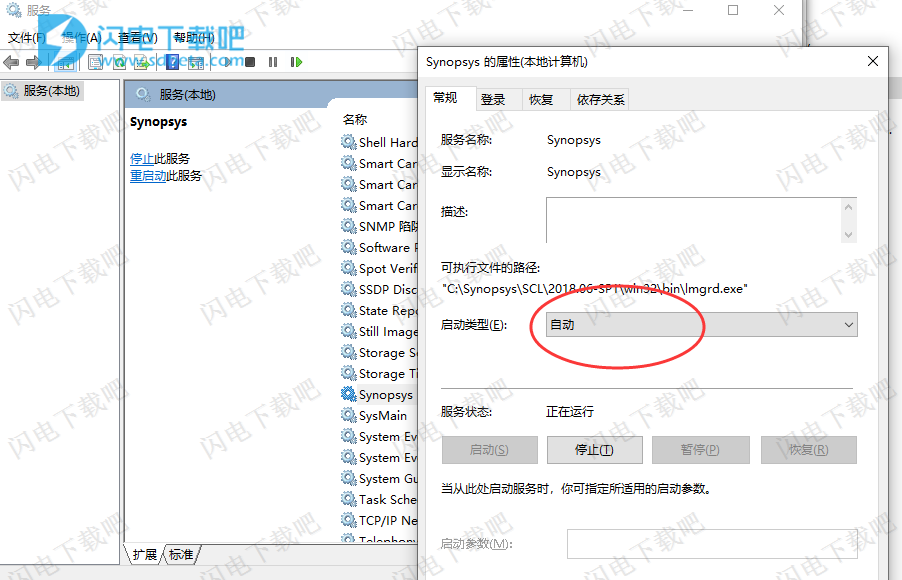

24、任务管理器找到Synopsys服务,右键点击打开服务,双击打开将“启动类型”选项设置为“自动”,然后从“恢复”选项卡中,将“重置失败计数之后”的值更改为1000。回到“常规”选项卡,单击“停止”,然后单击“确定”。

25、转到C:\synopsys\SCL\2018.06-SP1\win32\bin并打开lmtools.exe。转到“开始/停止/重读”选项卡,选中“强制服务器关闭”选项,然后单击“停止服务器”。等待作业完成,然后单击启动服务器,然后单击“重新读取许可证文件”并关闭lmtools

26、转到C:\synopsys\SCL\2018.06-SP1,用记事本打开Synopsys.dat文件,然后删除该行中的短语(大概)第8行(DAEMON snpslmd C:\synopsys\SCL\2018.06-SP1\win32\clear bin\snpslmd.exe)(确保没有空白行)。保存并关闭文件

27、转到C:synopsysSCL2018.06-SP1win32bin并打开lmtools.exe。转到“start/stop/reread tab”选项卡,选中“强制服务器关闭”选项,然后单击“停止服务器”。等待工作完成。然后点击启动服务器

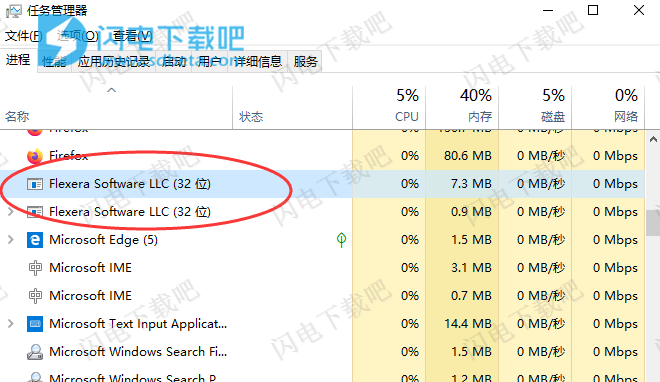

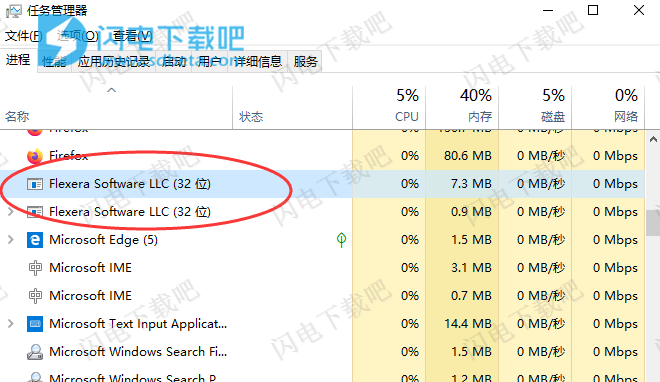

28、运行任务管理器,在backgrond进程部分中找到Flexera Software LLC(32位)项,右键单击并单击结束任务,关闭任务管理器

29、返回lmtools并单击启动服务器。转到“配置服务”选项卡,单击“view log”,然后单击“close log”。转到“start/stop/reread tab”选项卡,然后单击“ReRead License File”

30、现在运行任何FPGA软件并享受(请注意,启动时可能会遇到“许可证选择窗口”,只需选择您的首选许可证即可)

软件功能

1、快速的运行时间和增量功能,可在最快的时间内实现结果

2、最好的质量结果(结果质量)的性能调度的行业

3、逻辑到最小化的降低的成本和功率

4、提供多个目标的FPGA从一个单一RTL源

5、HDL分析仪原理观众对于快速调试和调整限制

6、通过比较FSM性能和来自ECC存储器的推断来减少SEU(包括重复TMR)的自动化

7、支持第三方FPGA

8、能力到调试操作FPGA直接在RTL代码

9、整合与Synphony模型编译器的实现算法的DSP

10、分析工具,以降低动态功耗消耗

11、支持基于原型的FPGA,包括门和时钟转换生成

12、支持的块建筑Synopsys的DesignWare的和的DesignWare核心的的数字,以确保兼容性ASIC当前

13、该设计为发展的分布和平行与流顶部至底部/自下而上或组合

14、自动化和定制,包括Tcl手和查找流

软件特色

1、高达4倍的综合运行时改进

现在,与使用单个处理器的传统逻辑综合相比,Synplify Premier的FAST逻辑综合模式可将速度提高多达4倍。新的编译点技术可通过在设计的不同部分自动执行并行时序驱动的综合执行来进一步提高速度,从而利用具有多个处理器核心的计算机。

2、使用新型全局放置器进行物理合成以提高结果质量

Synplify Premier中的新物理综合流程采用了Synopsys的全球布局技术,将性能改进应用于现有的布局布线设计。物理约束是根据先前的位置和路线自动确定的。通过使逻辑合成用户摆脱执行复杂的物理约束设置的需要,从而使其易于使用。

3、团队设计界面和自下而上的流程允许并行开发

Synplify Premier和Synplify Pro工具都集成了新的团队设计功能,用于分层项目管理和并行开发。可以在内部创建和共享设计模块或先前验证的设计IP。不需要进行平面规划,因此该流程易于使用。团队现在可以按层次管理和查看每个模块的设计实现结果和综合设置。设计团队成员可以拍摄块的快照,然后将设计文件传输给团队负责人,以将其整体集成到设计中。设计模块可以在RTL或EDIF级别上集成,从而节省时间,锁定性能并确保可预测的结果。

4、全面的DesignWare库支持基于FPGA的原型

Synplify Premier现在支持DesignWare库中的全套数据路径和构件块组件。Synplify Premier用户现在可以综合ASIC RTL,该RTL实例化DesignWare库的任何组件,以创建其ASIC设计的基于FPGA的原型,并获得性能优化的结果。ASIC和FPGA组件支持现已同步,以帮助确保原型中使用的相同DesignWare Library组件也用于ASIC中。

5、可用性

Synplify Pro和Synplify Premier产品的2010.09版本现已上市,维护中的现有客户可通过SolvNet从Synopsys直接获得。Windows和Linux,32位和64位平台均支持Synplify FPGA综合产品。

使用说明

一、逻辑综合设计流程

Synopsys FPGA工具通过首先将源代码编译成与技术无关的逻辑结构,然后优化逻辑并将其映射到技术特定的资源来合成逻辑。逻辑综合后,该工具将生成特定于供应商的网表和约束文件,您可以将其用作布局布线(P&R)工具的输入。

下图显示了用于逻辑综合的阶段和工具,以及一些主要的输入和输出。灰色显示的交互式计时分析步骤是可选的。尽管该流程将供应商约束文件显示为P&R工具的直接输入,但您应将这些文件添加到综合项目中以计时黑匣子。

逻辑综合程序

有关基于特定设计数据的分步说明的设计流程,请从http://solvnet.synopsys.com下载该教程。

以下步骤总结了用于综合设计的过程,下图也对此进行了说明。

1、创建一个项目。

2、将源文件添加到项目中。

3、设置设计的属性和约束。

4、在“实施选项”对话框中设置实施选项。

5、如果以逻辑综合模式运行Synplify Premier工具,则可以设置其他模式。有关详细信息,请参见设置综合策略。

6、单击运行以运行逻辑综合。

7、使用日志文件,HDL Analyst原理图视图,“消息”窗口和“监视”窗口之类的工具分析结果。

完成设计后,您可以使用输出文件通过供应商工具来运行布局布线并实现FPGA。

下图列出了流程中的主要步骤:

二、基于设计计划的逻辑综合

该流程使您可以使用布局图来指导逻辑综合。为此,您需要具有“设计计划器”选项的Synplify Premier软件(有关使用此工具的详细信息,请参阅“使用设计计划器进行平面布置”)。

下图显示了流程中使用的阶段和工具,以及一些主要的输入和输出。灰色显示的交互式计时分析,物理分析和反向注释步骤是可选的。

使用设计计划运行逻辑综合

通过这种方法,您可以使用“设计计划器”工具手动创建物理约束,以将关键路径逻辑分配给管芯上的特定位置以提高性能。然后,您可以使用该设计计划文件来约束逻辑综合。

下图显示了基于设计计划的逻辑综合流程。

1、设置项目并以逻辑综合模式编译设计。

2、分析时序结果。

分析时间安排。

确定要分配给区域的组件。

3、启动设计计划器工具(),然后执行以下操作:

为关键路径创建区域,并将关键路径交互分配给芯片区域。对于Intel FPGA(Stratix V器件)和Xilinx(UltraScale器件),请参见使用设计规划器(第2代)以获取详细信息。

为关键路径创建区域,并将关键路径交互分配给芯片区域。对于Intel FPGA(Stratix IV和Cyclone II及更低版本的设备)和Xilinx(Virtex-6及更低版本的设备),请参见Design Planner-使用区域以获取详细信息。

获得设计中每个RTL块的大小估计。有关详细信息,请参见检查利用率。

对于多个时钟,请将与每个时钟域关联的关键逻辑(不满足设计要求)分配给唯一的区域,以避免资源争用。

如果您的设计中有任何黑匣子,请将它们分配给一个区域。将该区域指定为IP块,以便Synplify Premier软件可以实例化网表文件中的黑盒。但是,您必须提供黑框的内容,以便布局和路由工具可以成功运行。

保存设计计划文件(dpf/sfp)并将其添加到您的项目中。

4、运行逻辑综合。

确保项目包括物理约束文件(dpf/sfp)。

将项目设置为在综合完成后自动运行布局布线。或者,您可以在独立模式下运行P&R工具。

综合工具遵循平面图文件中的区域放置约束。它将您在平面布置图中定义的每个区域都视为一个严格的层次结构,并且不会在此边界上进行优化。综合完成后,该工具将为目标技术生成一个结构化网表,并生成一个Tcl脚本,其中包含用于前向注释的信息,例如区域分配。

然后,该工具将启动P&R工具,并使用前向注释约束来指导P&R运行。

5、使用日志文件和分析工具来分析Synplify Premier工具中的计时。有关详细信息,请参见检查日志文件结果,在原理图视图中分析时序以及使用STA生成自定义时序报告。

如果达到目标,则可以继续进行P&R。如果没有,您应该重新评估时间安排和位置。