Active-HDL12ΤΤΫβΑφ ««Ω¥σΒΡFPGA…ηΦΤ¥¥Ϋ®ΚΆΖ¬’φIDEΘ§ «ΈΣVHDLΘ§Verilog/SystemVerilogΘ§EDIFΚΆSystemC…ηΦΤΒΡΩΣΖΔΕχ…ηΦΤΒΡΦ·≥…ΜΖΨ≥ΓΘΥϋΑϋά®ΦΗΗω…ηΦΤ δ»κΙΛΨΏΘ§HDL/SystemC±ύ“κΤςΘ§ΒΞΗωΖ¬’φΡΎΚΥΘ§ΦΗΗω±ξΉΦΚΆΗΏΦΕΒς ‘ΙΛΨΏΘ§ΆΦ–ΈΚΆΈΡ±ΨΖ¬’φ δ≥ω≤ιΩ¥ΤςΘ§“‘ΦΑ–μΕύ÷Φ‘ΎΦρΜ·…ηΦΤΘ§Ή ‘¥ΈΡΦΰΚΆΩβΙήάμΒΡΗ®÷ζ Β”Ο≥Χ–ρΘ§“‘ΦΑΡΎ÷ΟΫ”ΩΎΘ§‘ –μ‘Ύ±ΨΒΊΜρ‘Ε≥ΧΦΤΥψΜζ…œ‘Υ––ΡΘΡβΘ§ΉέΚœΜρ Βœ÷Θ§ΩΊ÷Τ‘¥ΈΡΦΰΒΡ–όΕ©Θ§Μρ”κΧαΙ©ΡΘΡβΡΘ–ΆΒΡΒΎ»ΐΖΫΙΛΨΏΫχ––Ά®–≈ΓΘ¥ΥΆβΘ§Active-HDLΧαΙ©ΝΥ“ΜΉιΙΠΡή«Ω¥σΒΡœρΒΦΘ§Ω…Αο÷ζ¥¥Ϋ®–¬ΒΡΙΛΉςΩ’ΦδΘ§…ηΦΤΜρ…ηΦΤΉ ‘¥Θ§Αϋά®VHDLΘ§VerilogΘ§SystemC‘¥ΈΡΦΰΘ§ΖΫΩρΆΦΜρΉ¥Χ§ΆΦΘ§≤β ‘ΤΫΧ®Β»ΓΘΡζΜΙΩ…“‘Ά®ΙΐActive-HDLΚξ”ο―‘ΒΡΟϋΝνά¥Βς”ΟΡζ¥”ΆΦ–Έ”ΟΜßΫγΟφ÷¥––ΒΡ¥σΕύ ΐ≤ΌΉςΓΘΆ®Ιΐ±ύ–¥Ή‘ΦΚΒΡΚξΘ§Ω…“‘œ‘Ή≈ΗΡ…Τ≤β ‘≤Δ Ι…ηΦΤ¥ΠάμΉ‘Ε·Μ·ΓΘActive-HDLΜΙΈΣPerlΚΆTcl/TkΧαΙ©Ϋ≈±Ψ“ΐ«φΓΘΆ®Ιΐ¥¥Ϋ®”ΟΜßΕ®“εΒΡΫ≈±ΨΘ§ΡζΩ…“‘Ά®ΙΐΧμΦ”ΤδΥϊ¥ΑΩΎΘ§ά©’ΙΚξ”ο―‘“‘ΦΑΈΣΆβ≤ΩΙΛΨΏΚΆ»μΦΰ≤ζΤΖΧαΙ©Ϋ”ΩΎά¥‘ω«ΩActive-HDL…ηΦΤΜΖΨ≥ΓΘActive-HDLΧΉΦΰΜΙΑϋά®VSimSAΘ§VSimSA «”Ο”Ύ≈ζ¥ΠάμΒΡΕάΝΔVHDL/Verilog/SystemVerilog/EDIF/SystemCΖ¬’φΜΖΨ≥ΓΘ‘ΎΙΠΡή…œΘ§VSimSAΆξ»ΪΕάΝΔ”ΎActive-HDLΓΘVSimSA”κActive-HDLΒΡ«χ±π‘Ύ”Ύ»±…ΌΆΦ–Έ”ΟΜßΫγΟφΘ®GUIΘ©ΓΘVSimSAΟϋΝνΚΆ≥Χ–ρΫω¥”ΟϋΝν––ΖΔ≤ΦΚΆΩΊ÷ΤΘ§’β‘ΎΉ‘Ε·Μ·…ηΦΤ≤β ‘÷–ΧΊ±π”–”ΟΓΘ»Ϊ–¬ΤΤΫβΑφœ¬‘ΊΘ§Κ§ΤΤΫβ≤ΙΕΓΈΡΦΰΘ§ΚΆ–μΩ…÷ΛΈΡΦΰΘ§”––η“ΣΒΡ≈σ”―≤Μ“Σ¥μΙΐΝΥΘΓ

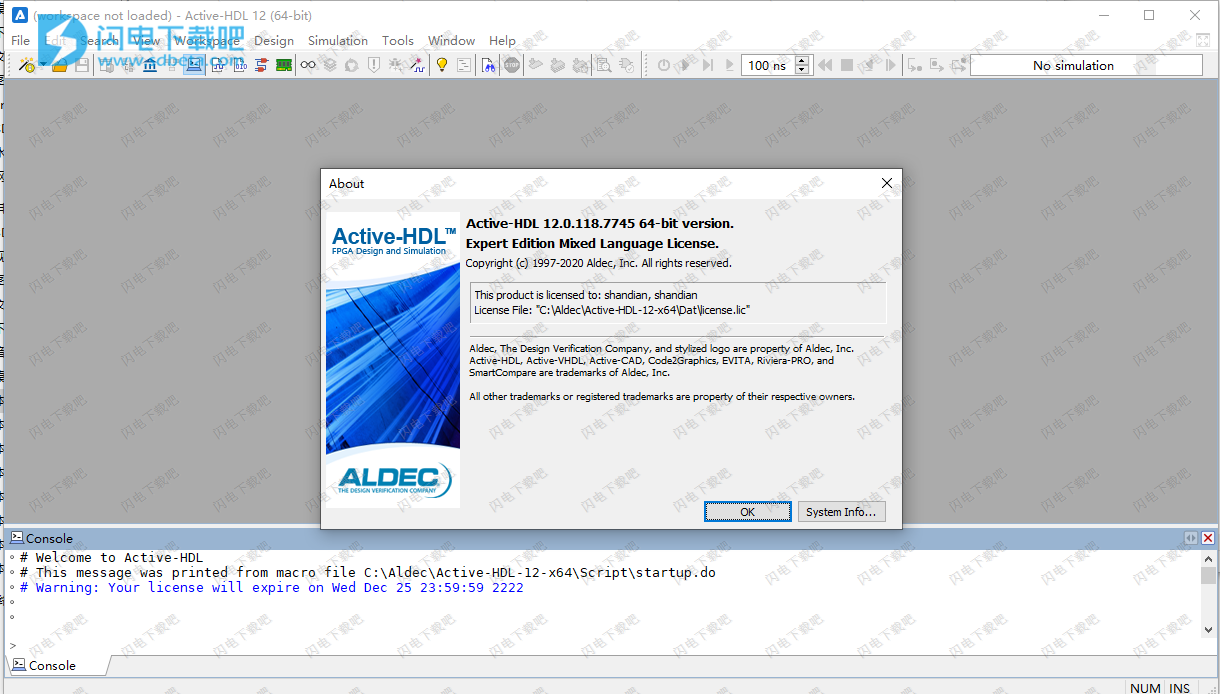

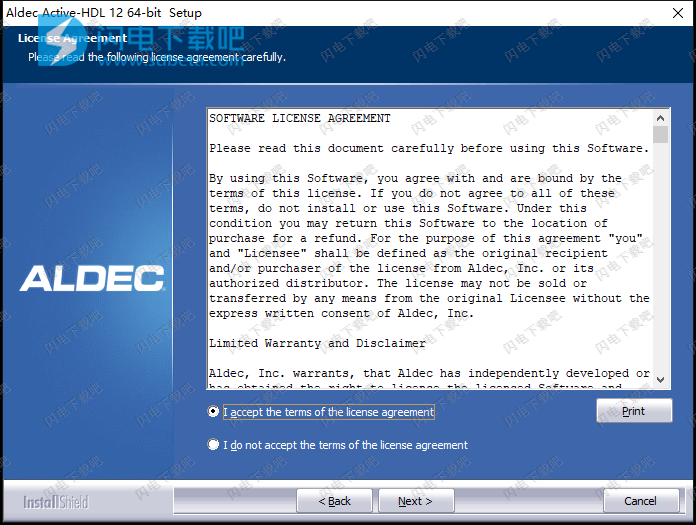

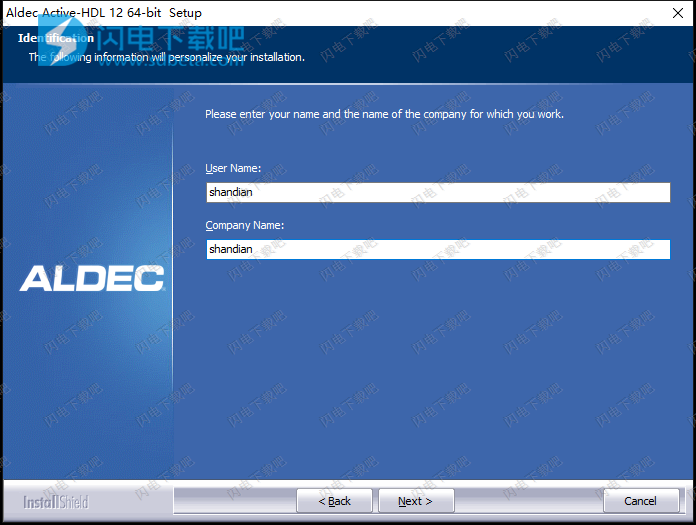

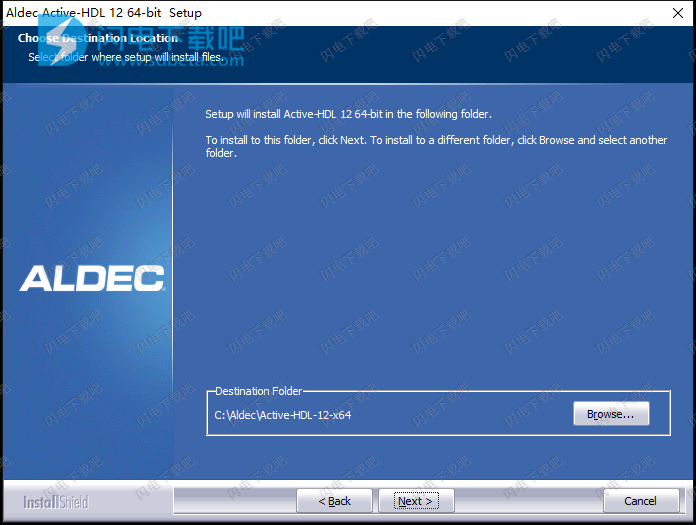

2ΓΔΥΪΜςActive-HDL_12.0.118.7745_x64_main_setup.exe‘Υ––Α≤ΉΑΘ§ Ι¥―ΓΈ“Ϋ” ή–μΩ…÷Λ–≠“ιΧθΩν

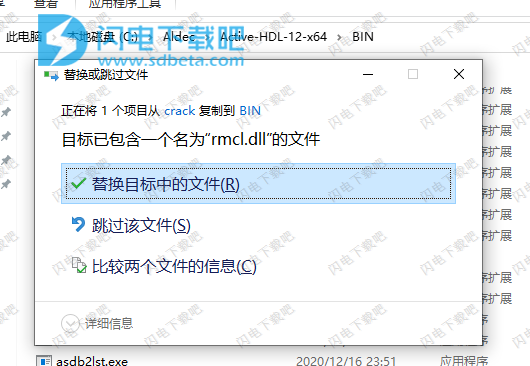

5ΓΔΑ≤ΉΑΆξ≥…Θ§ΫΪcrackœ¬ΒΡrmcl.dllΈΡΦΰΗ¥÷ΤΒΫΑ≤ΉΑΡΩ¬Φœ¬ΒΡbinΈΡΦΰΦ–÷–Θ§ΒψΜςΧφΜΜΡΩ±ξ÷–ΒΡΈΡΦΰ

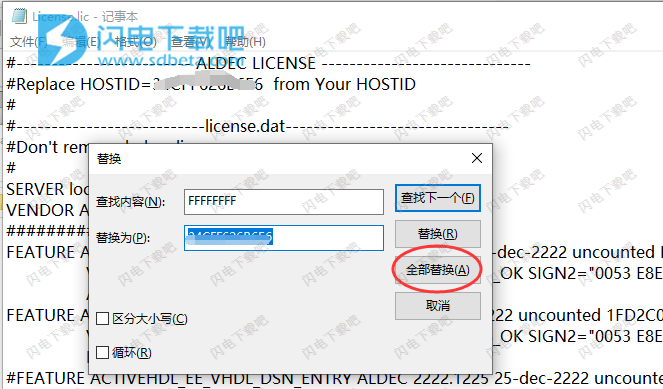

6ΓΔ“‘Φ« ¬±ΨΒΡΖΫ Ϋ¥ρΩΣlicense.licΘ§≤Δ Ι”ΟΡζΒΡMACΜρ“‘ΧΪΆχΒΊ÷ΖΫΪhostid="FFFFFFFF"÷–ΒΡFFFFFFFFΧφΜΜΒτΘ§ Ι”Ο±ύΦ≠-ΧφΜΜΘ§ΫΪΥυ”–ΒΡFFFFFFFFΕΦΧφΜΜΒτΘ§MACΜρ“‘ΧΪΆχΒΊ÷Ζ≤Μ“Σ¥χ“-”Θ§Άξ≥…Κσ±Θ¥φΘ®macΒΊ÷Ζ≤ι―·Θ§ Ι”Οwin+r, δ»κcmdΘ§»ΜΚσ‘ΎΟϋΝνΧα ΨΖϊ¥ΑΩΎ÷– δ»κipconfig /allΘ§ΒψΜςΜΊ≥ΒΦ¥Ω…Θ©

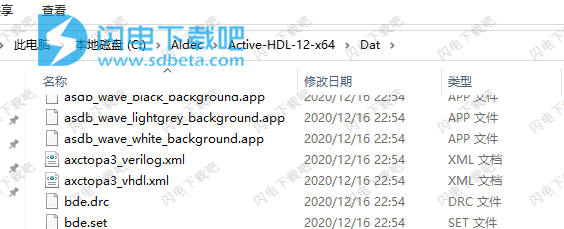

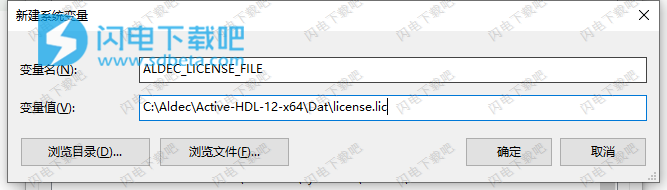

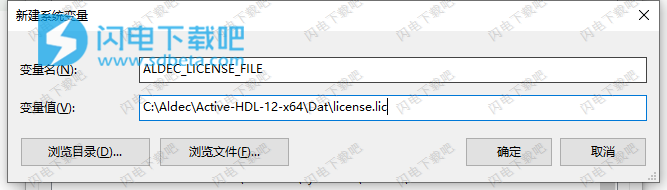

7ΓΔΫΪ–όΗΡΚσΒΡLicenseΗ¥÷ΤΒΫΑ≤ΉΑΡΩ¬Φ÷–Θ§άΐ»γΡ§»œC:\Aldec\Active-HDL 12 64-bit\Dat\license.lic

±δΝΩ÷ΒΘΚlicense.lic¬ΖΨΕΘ§άΐ»γΡ§»œC:\Aldec\Active-HDL-12-x64\Dat\license.lic

9ΓΔΆξ≥…Κσ‘Υ––≥Χ–ρœμ”ΟΦ¥Ω…

»μΦΰΙΠΡή

“ΜΓΔœνΡΩΙήάμ

FPGAœνΡΩΙήάμ

Βδ–ΆΒΡFPGA…ηΦΤΝς≥ΧΑϋά®…ηΦΤΫχ»κΫΉΕΈΘ§ΉέΚœΚΆ Βœ÷Θ®ΡβΚœ“‘ΦΑ≤ΦΨ÷≤ΦœΏ¥ΠάμΘ©Θ§ΟΩΗωΫΉΕΈΆ®≥ΘΥφΚσΫχ––Ζ¬’φΓΘ‘Ύ’ϊΗω…ηΦΤΝς≥Χ÷–ΙήάμœνΡΩ“‘ΦΑ…ηΦΤ ΐΨί±δΒΟΖ«≥Θ÷Ί“ΣΓΘ…ηΦΤΝς≥ΧΙήάμΤς «÷Φ‘ΎΉ‘Ε·÷¥––’β–©Ιΐ≥ΧΒΡΙΛΨΏΓΘΥϋ”κΒΎ»ΐΖΫΙΛΨΏΕ‘Ϋ”Θ§ΈΣFPGA…ηΦΤ»Υ‘±ΧαΙ©ΝΥ“ΜΗωΩ…‘Ύ’ϊΗωFPGA…ηΦΤΝς≥Χ÷– Ι”ΟΒΡΕάΧΊΤΫΧ®ΓΘ

ΝςΙήάμΤς

Ι”ΟFPGAœνΡΩΙήάμΒΡΚΟ¥ΠΘΚ

ΥϋΚ≠Η«ΝΥ¥”…ηΦΤΫχ»κΒΫ≤ΦΨ÷≤ΦœΏΒΡ’ϊΗωFPGA…ηΦΤΝς≥ΧΘ§’β“βΈΕΉ≈Ρζ≤Μ±Ί‘ΎFPGA…ηΦΤΒΡ≤ΜΆ§ΫΉΕΈ―ßœΑ≤ΜΆ§ΒΡΙ©”Π…ΧΙΛΨΏΓΘ

Υϋ”κ90Εύ÷÷Ι©”Π…ΧΙΛΨΏœύΝ§Ϋ”Θ§Ω…»ΟΡζ“‘Εύ÷÷≤ΜΆ§ΖΫ Ϋ≈δ÷ΟΝς≥Χ

Υϋ”κΑφ±Ψ/–όΕ©ΩΊ÷ΤœΒΆ≥–≠ΉςΘ§ΈΣΡζΒΡœνΡΩΧαΙ© ΐΨίΚΆΑφ±ΨΙήάμ

ΡΎ÷ΟΖΰΈώΤς≥Γ Ι…ηΦΤ»Υ‘±Ω…“‘ΙήάμΕ”Ν–“‘Ϋχ––Ζ¬’φΘ§ΉέΚœΚΆ Β ©»ΈΈώ

ΕΰΓΔΆΦ–Έ/ΈΡΉ÷…ηΦΤ δ»κ

1ΓΔ‘≠άμΆΦ/ΩρΆΦ±ύΦ≠Τς

ΩρΆΦ±ύΦ≠Τς «”Ο”ΎVHDLΘ§VerilogΚΆEDIF…ηΦΤΒΡΆΦ–Έ δ»κΒΡΙΛΨΏΓΘ»γΙϊΡζΒΡHDL…ηΦΤ‘ΎΚή¥σ≥ΧΕ»…œ «ΫαΙΙΜ·ΒΡΘ§Ρ«Ο¥”κ±ύ–¥‘¥¥ζ¬κœύ±»Θ§“‘ΆΦ–ΈΖΫ Ϋ“‘ΩρΆΦ–Έ Ϋ δ»κΤδΟη ωΩ…ΡήΜαΗϋ»ί“ΉΓΘ»ΜΚσΘ§≥Χ–ρΩρΆΦ±ύΦ≠ΤςΫΪΉ‘Ε·ΫΪΩρΆΦΉΣΜΜΈΣΫαΙΙΜ·ΒΡVHDLΘ§VerilogΜρEDIFΆχ±μΓΘ Ι”ΟActive-HDLΘ§ΡζΩ…“‘ΜλΚœΝΫ÷÷άύ–ΆΒΡΟη ωΓΘάΐ»γΘ§ΕΞ≤ψ…ηΦΤ ΒΧεΩ…“‘ «ΩρΆΦΘ§ΕχΤδ÷– Ι”ΟHDL¥ζ¬κ/EDIFΆχ±μΚΆ/ΜρΉ¥Χ§ΆΦΟη ωΤδ÷– ΒάΐΜ·ΒΡΉιΦΰΓΘ

Ι”Ο‘≠άμΆΦ±ύΦ≠ΤςΒΡΚΟ¥ΠΘΚ

‘≠άμΆΦ±ύΦ≠Τς÷ß≥÷Ή‘œ¬Εχ…œΚΆΉ‘…œΕχœ¬ΒΡΖΫΖ®

Ι©”Π…ΧΒΡ‘≠άμΆΦΩβ ΙΡζΩ…“‘¥¥Ϋ®ΟφœρΦΦ θΒΡΩρΆΦ

±ύΦ≠ΤςΒΡHierarchical τ–‘Ω…Αο÷ζΡζΈΣΗ¥‘”Ωι¥¥Ϋ®‘≠άμΆΦΒΡΕύΗω“≥Οφ

ΩρΆΦΈΡΦΰΩ…“‘ΉΣΜΜΈΣVHDLΘ§VerilogΜρEDIFΆχ±μ

2ΓΔΉ¥Χ§Μζ±ύΦ≠Τς

Ή¥Χ§ΆΦ±ύΦ≠Τς «“Μ÷÷ΙΛΨΏΘ§”Ο”ΎΕ‘Ά§≤ΫΜζΚΆ“λ≤ΫΜζΒΡΉ¥Χ§ΆΦΫχ––ΆΦ–Έ±ύΦ≠ΓΘΜφ÷ΤΉ¥Χ§ΆΦ «Ε‘Υ≥–ρ…η±ΗΫχ––Ϋ®ΡΘΒΡΝμ“Μ÷÷ΖΫΖ®ΓΘΡζΩ…“‘Ή‘ΦΚ δ»κ¬ΏΦ≠ΩιΒΡΟη ωΉςΈΣΆΦ–ΈΉ¥Χ§ΆΦΘ§Εχ≤Μ±ΊΉ‘ΦΚ±ύ–¥HDL¥ζ¬κΓΘ»ΜΚσΘ§±ύΦ≠ΤςΫΪΗυΨί δ»κΒΡΆΦ–ΈΟη ωΉ‘Ε·…ζ≥…HDL¥ζ¬κΓΘ”…”Ύ÷±ΙέΒΡΆΦ–Έ–Έ ΫΘ§Ή¥Χ§ΆΦ±»HDL¥ζ¬κΗϋ“Ή”Ύ―ßœΑ≤Δ«“Ω…ΕΝ–‘«ΩΓΘ

Ι”ΟΉ¥Χ§Μζ±ύΦ≠ΤςΒΡΚΟ¥ΠΘΚ

ΥϋΧαΙ©ΝΥ“ΜΗω÷±ΙέΒΡΒΊΆΦΘ§ΗΟΒΊΆΦ÷ΗΕ®ΝΥΉ¥Χ§÷°ΦδΒΡΝς≥ΧΘ§ ¬ΦΰΚΆΕ·ΉςΘ§’βΗϋ“Ή”Ύ‘ΡΕΝΚΆάμΫβΓΘ

ΡΎ÷ΟΒΡ≤β ‘Χ®…ζ≥…ΤςΩ…“‘Αο÷ζΡζΩλΥΌ―ι÷ΛΉ¥Χ§Μζ

ΥϋΩ…“‘‘Ύ…ηΦΤΜα“ιΤΎΦδ”ΟΉς≥ω…ΪΒΡ–≠ΉςΙΛΨΏΘ§“ρΈΣΥϋΟ«“Ή”ΎάμΫβΚΆΫβ ΆΓΘ

ΥϋΟ«Ω…”Ο”ΎΦ«¬ΦΗς÷÷≥ιœσΦΕ±πΒΡ…ηΦΤ

3ΓΔHDLΈΡΉ÷±ύΦ≠Τς

HDL±ύΦ≠Τς «…ηΦΤ”Ο”Ύ±ύΦ≠HDL‘¥¥ζ¬κΒΡΈΡ±Ψ±ύΦ≠ΤςΓΘΥϋ”κ±ύ“κΤςΚΆΡΘΡβΤςΫτΟήΦ·≥…Θ§“‘Ττ”ΟΒς ‘ΙΠΡήΓΘHDLΈΡ±Ψ±ύΦ≠ΤςΒΡ“Μ–©÷ς“ΣΙΠΡήΑϋά®ΙΊΦϋΉ÷ΆΜ≥ωœ‘ ΨΘ®VHDLΘ§Verilog/SystemVerilogΘ§C/C++Θ§SystemCΘ§OVAΚΆPSLΘ©Θ§Ε‘¥ζ¬κΉιΚΆ¥ζ¬κΫαΙΙΒΡ÷ß≥÷Θ§Ή‘Ε·Άξ≥…ΚΆΉ‘Ε·Ηώ ΫΜ·Θ§ ι«©ΚΆΟϋΟϊ ι«©Θ§“‘±ψ‘Ύ‘¥¥ζ¬κΘ§ΕœΒψΚΆΝ–―Γ‘ώ÷–«αΥ…ΒΦΚΫΓΘ

Ι”ΟHDLΈΡ±Ψ±ύΦ≠ΤςΒΡΚΟ¥ΠΘΚ

≤®–Έ≤ιΩ¥ΤςΚΆHDLΈΡ±Ψ±ύΦ≠Τς÷°ΦδΒΡΫΜ≤φΧΫ≤β ΙΒς ‘ΗϋΦ”»ί“Ή

Ω…“‘÷±Ϋ”¥”HDL±ύΦ≠ΤςΫΪ–≈Κ≈ΧμΦ”ΒΫ≤®–Έ≤ιΩ¥Τς

‘ΎΖ¬’φΙΐ≥Χ÷–÷ß≥÷‘¥¥ζ¬κ÷–ΒΡ Β ±÷ΒΧΫ’κ

VHDLΘ§VerilogΘ§SystemVerilogΚΆSystemCΒΡ”ο―‘ΡΘΑεΩ…Αο÷ζΩλΥΌ±ύ–¥¥ζ¬κ

4ΓΔCode2Graphics

Code2GraphicsΉΣΜΜΤς «“Μ÷÷ΙΛΨΏΘ§”Ο”ΎΫΪVHDLΘ§Verilog/SystemVerilogΚΆEDIFΆχ±μΉ‘Ε·ΉΣΜΜΈΣActive-HDL‘≠άμΆΦΚΆΉ¥Χ§ΆΦΓΘΥϋΖ÷ΈωVHDLΘ§VerilogΜρEDIFΈΡΦΰΘ§≤ΔΗυΨίΖ÷ΈωΈΡΦΰ÷–’“ΒΫΒΡ…ηΦΤ ΒΧεΘ§ΡΘΩιΜρΒΞ‘ΣΒΡ ΐΝΩ…ζ≥…“ΜΗωΜρΕύΗω‘≠άμΆΦΚΆΉ¥Χ§ΆΦΈΡΦΰΓΘ…ζ≥…ΒΡ‘≠άμΆΦΚΆΉ¥Χ§ΆΦΈΡΦΰΩ…“‘Ή‘Ε·ΗΫΦ”ΒΫ…ηΦΤΜρ±Θ¥φ‘ΎΒΞΕάΒΡΈΜ÷ΟΓΘ

Ι”ΟCode2GraphicsΒΡΚΟ¥ΠΘΚ

Υϋ¥”…ηΦΤ÷–Χα»Γ–≈œΔ≤Δ“‘ΆΦ–ΈΖΫ Ϋ≥ œ÷

RTL…ηΦΤΒΡΆΦ–ΈΩ… ”Μ·Ω…“‘¥σ¥σ‘ω«Ω…ηΦΤ÷Ί”ΟΙΐ≥Χ

Υϋ”–÷ζ”ΎΈΣΗ¥‘”ΒΡRTL…ηΦΤœνΡΩ¥¥Ϋ®ΆξΟάΒΡΈΡΒΒ

Ι”ΟΑο÷ζ

ΩρΦήΈΣΥυ”–ΉιΦΰΧαΙ©ΝΥΙΛΉςΩ’ΦδΚΆΙΒΆ®«ΰΒάΓΘ ≥ΐΝΥΖ¬’φΡΎΚΥΚΆ±ύ“κΤςΘ§ΟΩΗωActive-HDLΙΛΨΏΕΦ‘ΎΒΞΕάΒΡ¥ΑΩΎ÷– Βœ÷ΓΘ “‘œ¬ «Active-HDLΙΛΨΏΒΡΦρ“ΣΥΒΟςΓΘ

1ΓΔConsole

Alt + 0

ΩΊ÷ΤΧ®¥ΑΩΎ «“ΜΗωΫΜΜΞ ΫΒΡ δ»κ δ≥ωΈΡ±Ψ…η±ΗΘ§ΗΟ…η±ΗΘΚ

•ΧαΙ©Active-HDLΚξΟϋΝνΚΆ”ΟΜßΕ®“εΒΡΫ≈±ΨΒΡΧθΡΩ

• δ≥ω”…Active-HDLΙΛΨΏ…ζ≥…ΒΡœϊœΔΓΘ

2ΓΔΙΛΉς«χ/…ηΦΤδ·άάΤς

Workspace / Design Explorer”–÷ζ”ΎΙήάμActive-HDL…ηΦΤΘ§“‘±ψΡζ

≤Μ±ΊΒΘ–ΡΦΤΥψΜζ…œ…ηΦΤΈΡΦΰΒΡΈοάμΈΜ÷ΟΓΘ

3ΓΔ…ηΦΤδ·άάΤς

Alt + 1 / Alt + 2

“…ηΦΤδ·άάΤς”¥ΑΩΎœ‘ ΨΒ±«ΑΙΛΉς«χΚΆ…ηΦΤΒΡΡΎ»ίΘ§Φ¥ΘΚ

•ΙΛΉς«χΗΫ¥χΒΡ…ηΦΤ

•…ηΦΤΗΫ¥χΒΡΉ ‘¥ΈΡΦΰ

•…ηΦΤΒΡΡ§»œΙΛΉςΩβΒΡΡΎ»ί

•―Γ‘ώ”Ο”ΎΖ¬’φVHDLΘ§Verilog / SystemVerilogΒΡ…ηΦΤΒΞ‘ΣΒΡΫαΙΙ

4ΓΔ…ηΦΤΝς≥ΧΨ≠άμ

Alt + 3

…ηΦΤΝς≥ΧΙήάμΤς¥ΌΫχΝΥActive-HDL…ηΦΤΒΡΉ‘Ε·Μ·¥ΠάμΓΘ Υϋ“‘ΆΦ–ΈΆΦ–Έ Ϋœ‘ ΨΒδ–ΆΒΡ…ηΦΤΙΐ≥ΧΘ§ΆΦ÷–«Ε»κΒΡΑ¥≈ΞΩ…Βς”Ο≤Έ”κΗΟΙΐ≥ΧΒΡ”Π”Ο≥Χ–ρΓΘ

5ΓΔ”ο―‘÷ζ ÷

”ο―‘÷ζ ÷ «“ΜΗωΗ®÷ζΙΛΨΏΘ§ΥϋΧαΙ©–μΕύVHDLΚΆVerilogΡΘΑεΘ§ΥϋΟ«Ε‘Βδ–ΆΒΡ¬ΏΦ≠‘≠”οΚΆΙΠΡήΩιΫχ––Ϋ®ΡΘΓΘ Υϋ”κHDL±ύΦ≠ΤςΦ·≥…‘Ύ“ΜΤπΘ§“ρ¥ΥΡζΩ…“‘ΫΪΥυ–ηΒΡΡΘΑεΉ‘Ε·≤ε»κ“―±ύΦ≠ΒΡ‘¥ΈΡΦΰ÷–ΓΘ ”ο―‘÷ζ ÷ΜΙ‘ –μΡζΕ®“εΉ‘ΦΚΒΡΡΘΑεΓΘ

6ΓΔHDL±ύΦ≠Τς

HDL±ύΦ≠Τς «ΈΣHDL‘¥ΈΡΦΰ…ηΦΤΒΡΈΡ±Ψ±ύΦ≠ΤςΓΘΥϋ“‘≤ΜΆ§ΒΡ―’…ΪΘ®ΙΊΦϋΉ÷―’…ΪΘ©œ‘ ΨΧΊΕ®ΒΡ”οΖ®άύ±πΓΘΗΟ±ύΦ≠Τς”κΡΘΡβΤςΫτΟήΦ·≥…Θ§Ω…“‘Βς ‘‘¥¥ζ¬κΓΘΒ± Ι”ΟHDL Editor±ύΦ≠ΚξΈΡΦΰΘ§PerlΫ≈±ΨΚΆTclΫ≈±Ψ ±Θ§ΙΊΦϋΉ÷Ή≈…Ϊ“≤Ω…”ΟΓΘ

7ΓΔΉ¥Χ§ΆΦ±ύΦ≠Τς

Ή¥Χ§ΆΦ±ύΦ≠Τς «…ηΦΤ”Ο”Ύ±ύΦ≠Ή¥Χ§ΜζΆΦΒΡΆΦ–ΈΙΛΨΏΓΘ±ύΦ≠ΤςΜαΉ‘Ε·ΫΪΆΦ–ΈΜ·…ηΦΤΒΡΆΦ±μΉΣΜΜΈΣVHDLΜρVerilog¥ζ¬κΓΘ

8ΓΔ≤®–Έ≤ιΩ¥Τς/±ύΦ≠Τς

≤®–Έ≤ιΩ¥Τς/±ύΦ≠ΤςΫΪΖ¬’φΫαΙϊœ‘ ΨΈΣ–≈Κ≈≤®–ΈΓΘΥϋ‘ –μΡζ“‘ΆΦ–ΈΖΫ Ϋ±ύΦ≠≤®–ΈΘ§“‘¥¥Ϋ®Υυ–ηΒΡ≤β ‘ ΗΝΩΓΘ

9ΓΔ≥Χ–ρΩρΆΦ±ύΦ≠Τς

ΩρΆΦ±ύΦ≠Τς «“Μ÷÷ΆΦ–ΈΙΛΨΏΘ§÷Φ‘Ύ¥¥Ϋ®ΩρΆΦΓΘ±ύΦ≠ΤςΜαΉ‘Ε·ΫΪΆΦ–ΈΜ·…ηΦΤΒΡΆΦ±μΉΣΜΜΈΣVHDLΜρVerilog¥ζ¬κΓΘ

10ΓΔΝ–±μ

“Ν–±μ”¥ΑΩΎ“‘±μΗώΈΡ±ΨΗώ Ϋœ‘ ΨΡΘΡβ‘Υ––ΒΡΫαΙϊΓΘΥϋ ΙΡζΡήΙΜ“‘‘ωΝΩ÷ήΤΎΨΪΕ»ΗζΉΌΖ¬’φΫαΙϊΓΘ

11ΓΔ ÷±μ

Alt + 4

Φύ ”¥ΑΩΎœ‘ ΨΡΘΡβΙΐ≥Χ÷–Υυ―ΓVHDLΜρVerilogΕ‘œσΒΡΒ±«Α÷ΒΓΘ

12ΓΔΒς”ΟΕ―’Μ

Alt + 6

“Βς”ΟΕ―’Μ”¥ΑΩΎ «“ΜΗωΒς ‘ΙΛΨΏΘ§Υϋœ‘ ΨΒ±«Α’ΐ‘Ύ÷¥––ΒΡΫχ≥Χ÷–’ΐ‘Ύ÷¥––ΒΡΉ”≥Χ–ρΘ®≥Χ–ρΚΆΚ· ΐΘ©ΒΡΝ–±μΓΘ

13ΓΔΆΦ ιΙίΨ≠άμ

Alt + 7

ΩβΙήάμΤς÷Φ‘ΎΙήάμActive-HDLΩβΦΑΤδΡΎ»ίΓΘ

14ΓΔΦ«“δΧεΦλ ”

Alt + 9

``ΡΎ¥φ ”ΆΦ''¥ΑΩΎ «“Μ÷÷Βς ‘ΙΛΨΏΘ§÷Φ‘Ύœ‘ Ψ…ηΦΤ÷–Ε®“εΒΡΡΎ¥φΡΎ»ίΘ®άΐ»γΕΰΈ§ ΐΉιάύ–ΆΒΡΕ‘œσΘ©ΓΘ

15ΓΔΖΰΈώΤς≥Γ

ΖΰΈώΤς≥Γ «‘ΎΨ÷”ρΆχ…œ‘Υ––ΒΡΗΏΦΕΕάΝΔΙΛΨΏΘ§Υϋ Ι”ΟΜßΩ…“‘ΦΤΜ°»ΈΈώΘ§»ΜΚσ‘ΎΆχ¬γ…œΩ…”ΟΒΡ―ΓΕ®ΦΤΥψΜζ…œΉ‘Ε·÷¥––»ΈΈώΓΘ

16ΓΔ¥ζ¬κΗ≤Η«¬

¥ζ¬κΗ≤Η«¬ «“ΜΗω≥Χ–ρΘ§Ω…»ΟΡζ≤β ‘≤β ‘ΤΫΧ®≤Δ»ΖΕ®»γΚΈ÷¥––‘¥¥ζ¬κΓΘ

17ΓΔ…ηΦΤΖ÷ΈωΤς

Design Profilerœ‘ ΨΝΥΖ¬’φΤς‘ΎΖ¬’φΙΐ≥Χ÷–Μ®Ζ―ΒΡ ±ΦδΘ§≤Δ…ν»κΝΥΫβΝΥCPUΒΡ Ι”ΟΖΫ ΫΓΘ

18ΓΔ‘¥¥ζ¬κΑφ±ΨΩΊ÷Τ

“ΜΗω‘ –μΡζ”κΆβ≤ΩΉ®“ΒSource Revision ControlœΒΆ≥Ϋχ––Ά®–≈ΒΡΫγΟφΓΘ ΡΎ÷ΟΫ”ΩΎ‘ –μ÷±Ϋ”‘ΎActive-HDLΜΖΨ≥÷–Ε‘‘¥ΈΡΦΰΒΡ‘γΤΎΑφ±ΨΫχ––≤ΌΉςΓΘ

19ΓΔC¥ζ¬κΒς ‘

Alt + 8

C¥ζ¬κΒς ‘―Γœν‘ –μΒς ‘ΉςΈΣHDL…ηΦΤ“Μ≤ΩΖ÷ΒΡPLI / VHPI”Π”Ο≥Χ–ρΘ®DLLΘ©ΓΘ

20ΓΔΗΏΦΕ ΐΨίΝς

‘ –μ‘Ύ…ηΦΤ÷–ΧΫΥς≤ΔΖΔ”οΨδΒΡΝ§Ά®–‘Θ§≤Δ‘ΎΖ¬’φΙΐ≥Χ÷–“‘ΆΦ±μΒΡ–Έ Ϋ≥ œ÷ΓΘ

21ΓΔΕœ―‘≤ιΩ¥Τς

Εœ―‘≤ιΩ¥Τς¥ΑΩΎœ‘ ΨΝΥ‘ΎΡΘΡβΙΐ≥Χ÷–’κΕ‘OVAΘ§PSLΜρSystemVerilogΕœ―‘ΚΆCover”οΨδ ’Φ·ΒΡΆ≥ΦΤ–≈œΔΓΘ

22ΓΔCode2GraphicsΘ®TMΘ©ΉΣΜΜΤς

Ctrl + B

Code2GraphicsΘ®TMΘ©ΉΣΜΜΤς «“Μ÷÷”Ο”ΎΫΪVHDLΘ§VerilogΜρEDIF‘¥ΈΡΦΰΉ‘Ε·ΉΣΜΜΈΣActive-HDLΖΫΩρΆΦΚΆΉ¥Χ§ΆΦΒΡΙΛΨΏΓΘ