Riviera-PRO�ƽ���Ǿ�������������֤�ĸ���������������Ƽ��FPGA��SoC�豸���棬Ϊ����ʦ�Ǵ����˸���Ŀ����ԣ��Ը��ּ�����ս�ĸ��ӵ�ϵͳ�Ŀ�����ƺ���֤�������ṩ�˸���İ�������Ϊ�������˻��ڱ���VHDL��SystemVerilog��SystemC֧�֣�����ҵ�����ȵ������ع������������ɵĶ����Ե��Ի�����ȫ��Ļ��ڶ��Ե���֤��SVA��PSL���������븲���������Ƿ������ߣ��Լ���UVM��OS-VVM��UVVM��Cocotb��Vunit�����ڸ���֤���Եķ����ȣ���Щ���������ص����ƣ������е�һ�ж���ȫ�漤�����Ĵ�����������߹���ʦ��רҵˮƽ���������Ƶ��Զ������ܣ�ȫ����������������ٴ���IJ����������ƵĿ����ԣ����̵�������Ҫ��ʱ�䣬��ȷ�����ٵķ������������ƽ�汾������Ҫ�����Ѳ�Ҫ�����ˣ�

��װ����̳�

1�����ؽ�ѹ���ļ�����ͼ��ʾ

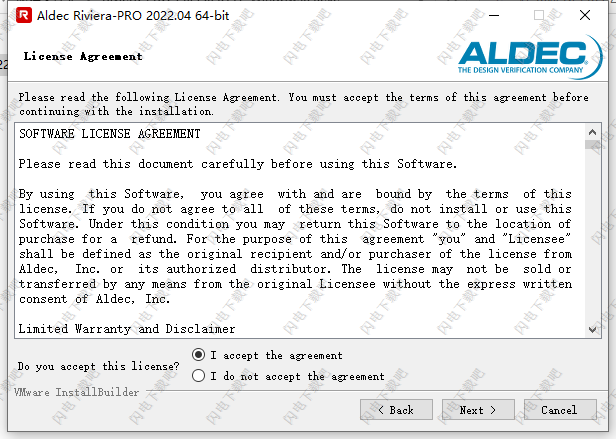

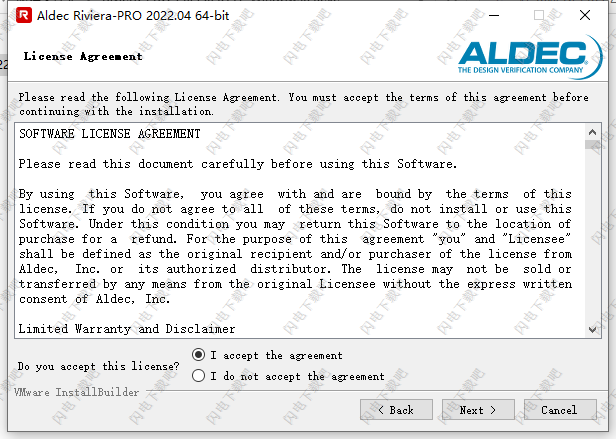

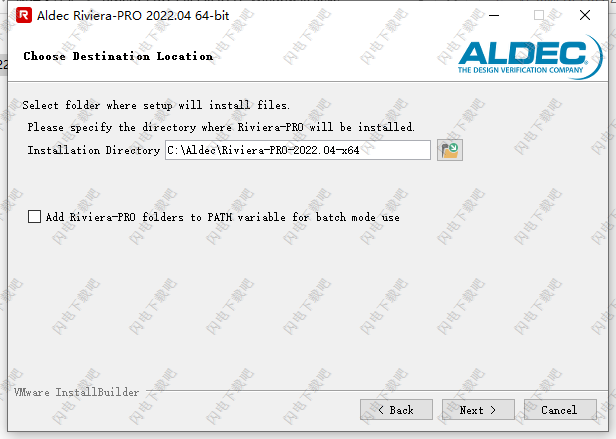

2���Ȱ�װ��������ѡ����ѡ��

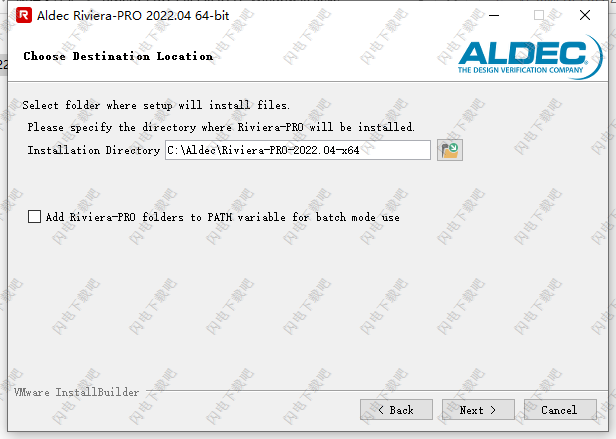

3����װ����

4����ɺ�Ҫ��������patched�е��ļ����Ƶ�������װĿ¼�в������滻

5��Ȼ��������Ҫ��rivieraall.dat���Ƶ���������֤�����㣨����C:\flexrm\rivieraall.dat��������ϵͳ��������ALDEC_LICENSE_FILE=C:\flexlm\rivieraall.dat

6������Riviera pro����

��������

1�������ܷ���

Riviera PRO�����ҵ�����ȵ�ģ���Ż��㷨���ڻ������ģ����ʵ��������ܡ������ҵ���ȵ�������Riviera PRO�ܹ�ʵ�ָع������������ڿ�����ӵ�ϵͳ��

2��������

���ɵĶ����Ե��Ի���ʹ��ʱ����Ʒ��������Զ�������������������֧�����б����ԣ����ṩֱ�۵ķ�ʽ�����ӻ��ͷ�������еĹؼ��������õ��Թ����ṩ������١����Ρ��������������ʡ����ԡ�UVM���ڴ���ӻ����ܡ�

3����ҵ���Ͷ�ʻر���

Riviera PROʹAldec�ͻ��ܹ��ڸ��̵�ʱ�����Ը��͵ijɱ��ṩ���²�Ʒ��Aldec��֮��Ч������Զ������������ͻ��ӿ�������ҽ�ơ����պ���;���Ӧ�ò�Ʒ����ƺ�ʵʩ������EDA���߰��Լ�ȫ�����ѵ��֧���⣬Aldec��Ͷ���ڽ���������ƺ���֤��������ĺ�������ϵ�ͼ��ɡ�

�¹���

1��Aldec��Inc.��FPGA��SoC��ƻ��HDL���Է����Ӳ��������֤���������Ƴ������°汾��Riviera-PRO��ΪVersal™����Ӧ�������ƽ̨��ACAP����Ƶ�ϵͳ�����ṩ֧�֡�

2��Versal ACAP��Xilinx/AMD��������һ��ͻ���Ե�����Ӧƽ̨�������˹��������棨AIE��������ϵͳ��PS�����ɱ������PL����Ƭ�����磨NoC����ǿ�������ض�IP�������DMA��CCIX��PCIe Gen5��HBM��600G�������Ϻ�600G��̫����Versal ACAP֧�ָ����㷨���칹���㣬�����ٹ������أ������˹����ܡ�Ƕ��ʽ��������ܼ��㡣

3��Riviera-PRO֧�ֻ���Vitis™Ӳ���������̵�Versal ACAP���ϵͳ���棬���ڲ���AIE��PS��PL֮��Ľ���������Ӳ���������ú�ϵͳ���ɶ�����Vitis��������ɵġ�VitisΪͼ��Ӧ�ó�������AIEģ������ΪPL�ں�����Riviera-PROģ������ΪPS����Ӧ�ó�������QEMU����Դϵͳ����������SystemCģ��Ҳ������AIE��NoC��Ҳ������Riviera-PRO�н���ģ�⡣

4��ϵͳ��������κ�Versal ACAP��ƶ�������Ҫ����Ϊ�����и��ӵ���Ӧ�Լܹ������ܶȡ�������ϵͳ��ƿ�������Ŀ���ڵ���������ȫ���Կɼ��Խ��в��ԣ��������κ�����Ӳ�����Ӷ������ɵ����и�����Գ��������Լ�������͵��Ը������⡣

5���û���������Riviera-PRO�ĸ����ܻ��HDL�������棬ʹ�ò��β鿴���ĸ����Ի���������������RTL��νṹ������鿴���Լ���֤�����ʹ��ܣ�����븲���ʺ��ܸ����ʡ�Riviera-PRO��SystemVerilog��UVM��ȫ��֧����������Ҫ���������ú��Ӳ���ƽ̨�������û���

6��AldecӪ���ܼ�Louie De Luna��ʾ��“Versal ACAP�ܹ���FPGA������и��������壬���칹�������Ϸ����ı��ߡ�“����Versal���û������Զ����Լ����ض�����ܹ������Ż����ض��������صļ��㡣�����������ڲ������ʱ�������컯��ͨ��Ӳ��������������ɵġ�

7�������FPGA��Ŀ����������һ����Ҫ�Ĵ������ݵ������ж����������������ڷ������֤������ȵؼ��ٴ������ݵĹؼ����档ϵͳ���������ִ���㷨��֤����֤�ܹ����ơ����ӵ�Ӳ��ƽ̨��Ӧ��������

8���������ʹ��Riviera-PRO��ΪVitisӲ���������̵�RTLģ�����ļ���Versal ACAP�̳���ƺͲ��������Aldec��Github���ҵ���

9��������ά����-PRO™

Riviera-PRO™�����˹���ʦ����δ�����FPGA��SoC��������֤���ù���ͨ����ϸ����ܷ������桢��ͬ����ĸ����Թ����Լ����������Ժ���֤�����֧�֣�ʵ�������յIJ���ƽ̨���������������Ժ��Զ�����

ʹ��˵��

1��ΪRiviera-PRO����Ӣ�ض�®Quartus®Prime�����

����

�û�����ʹ�ñ���������Ӣ�ض�®Quartus®Prime�����б���Riviera-PRO�⡣���ڱ�Ӧ��˵����Ŀ�ģ�����ʹ����Quartus®Prime�����ṩ��ͨ��Riviera-PRO 2021.10��·����

�������

��Quartus®Prime��

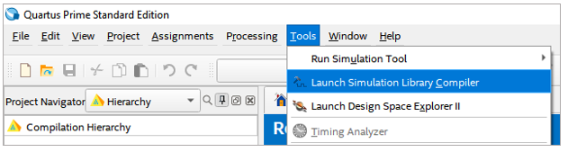

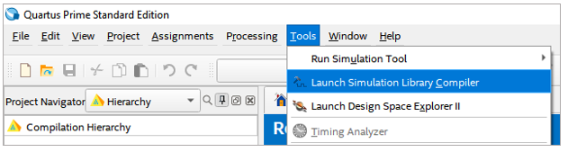

ת��“����”|”����������������

ͼ1������������

EDAģ������������

ѡ�������µ���ά����-PRO���ڿ�ִ���ļ�λ���ֶ��£��ṩriviera.exe�ļ���·����

ͼ2���������������������ƺ�λ��

ѡ��Ҫ����Ŀ�ϵ�У�Ȼ��ѡ������ԡ�

ע�⣺>���Ž�ѡ����ѡ����壬>>���Ž�ѡ�����п��õ��塣

ͼ3��EDA��������������ѡ��

Ϊ�ѱ���Ŀ�ѡ�����Ŀ¼��

ͼ4�����������������Ŀ¼

ָ���������ú�ѡ��“��ʼ����”��

ͼ5����������������ʼ����

����ɹ��������Թر�EDAģ�����������ڡ�

ͼ6���ɹ�����

2����ʼʹ��Riviera-PRO��OSVVM��

����

OSVVM ��һ�����ܲ���ƽ̨������������“���ܸ���”�붨���㷨�������ļ���Լ��������������ʹ�á�OSVVM��ָ��������֤VHDL�ļ��ɻ�����OSVVM ����“��Դ VHDL ��֤����”��OSVVM��һ��VHDL�������������Aldec��Synthworks������OSVVM �ɰ�����ʹ�� VHDL �����ִ�Լ�������֤����������OSVVM�����Խ�����֤�������ӵ��䵱ǰ�IJ���ƽ̨�У�������ѧϰ�����Ի��������еIJ���ƽ̨ģ�͡����̳��ṩ���й�ʹ�� OSVVM for VHDL �Ļ������ܵ�˵���� OSVVM ֧�ֵĹ��������������֤�����Ĺ�����ͬ�����������ģ��Լ���������ɣ����ܸ��ǣ���Ϣ���ˣ��Ƿְ��FIFO������ȡ�

Ϊʲôѡ��OSVVM��

��֤�����ڸ�������ж���һ�������⡣��֤�͵���������DZȱ�д��ƴ�����ѡ���System Verilogһ����ֱ����VHDL�б�д�����׳�����OSVVM �ṩ��һ�ַ����Ϳ⣬�ɼ� VHDL �û���������֤������OSVVM�����������Ա���Դ�һ�����Ժͷ����л�ù��ܣ����Ժͼ���ԡ�

��ʼ

��Riviera-PRO�п�ʼʹ��OSVVM�ĵ�һ����ȷ����ʹ�õ���VHDL 2008����߰汾������ʹ��Riviera-PRO�����ģ��ߵ��û������ܱ���ר�Ŵ�OSVVM��վ����OSVVM��

��Ҫ����Ĺؼ����������°��������������ӵ��κ� OSVVM ����У���Ϊ����ʾ��Ҫ�� OSVVM �����

library osvvm;

use osvvm.RandomPkg.all;

use osvvm.CoveragePkg.all;

ͼ�����Ϣ��

���Pkg

RandomPkg ʹ����Ϊ RandomPType ���ܱ�������ʵ������������ܡ�ʹ���ܱ����������������Ӵ洢���ܱ��������ڲ����ⷴ����������ʹ�ú�������������Ҫʹ�� RandomPkg�����ȱ������� OSVVM ��� RandomPkg��������ʾ��

library osvvm;

use osvvm.RandomPkg.all;

��Ҫִ������������̱��������Լ��ľֲ������������ÿ��ִ��������Ĺ��̶���Ҫ�Լ���������������ñ�������Ψһ������ֵ��ִ�д˲�����һ�ּ������������̲�ʹ�� RV'instance_name ��Ϊ Initseed �IJ��������� RV��InitSeed��RV'instance_name��;��.�������ͨ�����غ���֮һ��ɵģ����� RandInt������ RandInt ��= RV��RandInt��0,255��;��.

���Ƿ�ΧPkg

CoveragePkg��Perl Art Open Source License�·�����������ѵġ������Դ� http://www.synthworks.com/downloads �����������ʱ���¡�Ŀǰ������ƻ����� CoveragePkg ������д���ܸ��ǡ�ʵ���ϣ����ܸ��ǿ���ʹ���κδ����д��CoveragePkg ������������ڼ���������Թ��ܸ��ǽ��н�ģ�Ļ������������������ʶ�����������ģ�͡��ۻ������ʡ��븲�������ݽṹ�����Լ����渲���ʡ����Ƿ�Χ��ʹ�ô洢�ڸ��Ƿ�Χ�����ڲ������ݽṹ��ģ�ġ������ʶ�����ͨ������ CovPType ���͵Ĺ������������ģ�������ʾ��

architecture Test of tb is

shared variable CovBin1 : CovPType;

Լ�������֤

Լ�������֤����ʱ��Ϊ����ƽ̨�Զ������������ڸ�����֤�����б�����С�Լ�������֤�Ļ���˼����ʹ���������Ϊ��֤�����Ļ�������ͳ����ʹ����ν��“����”���� - ����д���Ե��˱���ȷ����Ӧ��ʲô�̼���Լ�������֤ʹ��������롣���кܶ�ô���

���ģ��ʱ��Խ����������ɸ���IJ���������

�����ܻᷢ�����������������ϻ˵�����ֵ�����µĴ���ͨ��������ԣ���������������������̫�����ˣ���������ͼ�����㲻ϣ�����������顣

�����Զ����Ժ����Կ����ڶ�����ԡ�

Լ��������Ե���Ҫȱ��������Ҫ��һ���Լ����ƽ̨���ŵ����Լ����ƽ̨����֤����ϵͳ�ĺ÷�����������Ҫ��ӵ�б�����ƣ�DUT���IJο�ģ�͡� ���ǵ��������н��ͣ���Ȼ����һ�����⡣������˵��“��Լ��”һ����ʲô��˼���������������� DUT �IJ�����������ˣ�������ˣ�����֪��ʲôû�о������ԡ�Ϊ�˱����������������ÿ�����Ե㣬����ʹ��ijЩԼ����Ҳ��Ϊ���ܸ��ǣ�������������������ܸ����ʺ������ض��淶����ص����ݣ��Ը������Ƿ��Ѻ��Ǹù淶�㡣��ע�⣬������븲���ʲ�ͬ�����븲����ֻ�Ǹ������Ƿ�ִ����ÿһ�д��� - ���빦���ء���ʹÿ�д��붼��ִ�У����� DUT Ҳ���ܲ���ȷ��OSVVM �ṩ��һ���ռ���֤�����нڵ�ֵ�ķ�����������ȷ����֤��ʱ��ɡ�

�������ֵ

Ϊ���������ֵ��������Ҫ���ĵ�һ�����ǰ����ʵ��İ�������

library osvvm;

use osvvm.RandomPkg.all;

use osvvm.CoveragePkg.all;

Next, we declare variables of the appropriate types.

variable a1 : RandomPType;

variable b1 : RandomPType;

�����������Ǵ������ֵ��

A <= a1.Randslv(0,255,8);

B <= b1.Randslv(0,255,8);

����ļ�����ʾ����δ��� 8 λ���������ֵ����ֵ��������ΧΪ 0 �� 255��

ͼ1.����˵��

����Լ���ͷֲ�

�����ʾ����������Χ������ֵ���������ǿ���ϣ�������������Ϊ�ض���Χ��ֵ��RandomPType ��������ȷָ��Ҫ���ɵ�ֵ����ֲ���

abc <= Rndabc.Randslv(0,31,4);

def <= Rnddef.Randslv((0,1,2,3,5,7,9,11,17,23,29,31),4);

��һ��ʾ����ʾ�� 0 �� 31 ������Χ�ڵĻ���������� �ڶ���ʾ���������������ʾ���Ѿ��ṩ��Լ�����Ҳ���ʾ�� 4 λ�Ŀ��ȡ� ��ˣ�������������ѡ����Բ���VHDL����ƽ̨�е��������Լ���ͷֲ���

���ܸ���

���ܸ������ǹ۲���Լƻ�ִ������Ĵ��롣��ˣ�����д�Ĵ������ڸ����Ƿ�ִ��������ƻ�ӿ�Ҫ���ܻ�߽��������Ӧ����Ҫֵ��ֵ����ֵ���С����û�й��ܸ��ǣ����Ͳ�֪��������Ժ�������Щ����㣬����Ҫ���ǣ�����֪����Щ����δ���ǡ� Ϊ�����ɹ��ܸ����ʣ����Dz������ǵ㡣���ǵ�����������ǽ�����ֵ���������еĹ��ܡ����ܸ��ǻ����Ϸ�Ϊ3���Ρ�I�� ���ã�ii�� ������ iii�� ���渲�Ƿ�Χ�����ǵ������ֵ���в������ڲ��������У��Ը��Ƿ�Χ���в��������ģ��ֹͣʱ�����汨����̻�д�������ĸ��������ݡ�

���������������

����ά����-PRO�У�������Ƽ�����Դ���������һ����Ϊ������������������ͬʱ���Ӻʹ��������ơ�

ת��“�ļ�”|”�½���Ȼ�����������µĹ�������������

���빤�������ƣ�Ȼ��ѡ��Ҫ�����д�����Ŀ��λ�á�

��� OK ��ɺ�İ�ť��������ͼ��

ͼ2.�����¹�����

�������¹������������Ҽ�����������ѡ�Ȼ��ת������ |����ơ����������´��ڡ�

ͼ3.���������

��ɺ�“���”��ť��

��ƹ�����������ʾ���������ƺ��ӵ�����ơ�

ͼ4.“��ƹ�����”����

����/�����ļ������

Ҫ�������ļ��������ļ���Ŀ¼��������ƹ������е�������λ�ã�Ȼ��“���� |�½��ļ���

��Ҳ����ʹ��“�ļ�”|”�²˵������ļ������䱣�浽���Ŀ¼����ͼ��

ͼ5.����/�����ļ������

���� HDL Դ����

���Ҫ���� VHDL/Verilog/System C Դ�ļ�����˫��“���� |�½��ļ�ѡ����ǣ����������ṩ��OSVVM FIFOʾ��ʵ�֣���������Ѿ����˸��ļ�����������ѡ�������� |�����ļ�������ʵʩ������ļ���

���

�����Ƕ�Դ�ļ����з����Ĺ��̡��ļ��а����ķ�����Ƶ�Ԫ��ģ������������ĸ�ʽ���빤�����С�

�����ļ�

���Ҫ���뵥���ļ�����ת�� ��ƹ����� �е� �ļ� ���Ҽ��������ļ���Ȼ��ӿ�ݲ˵���ѡ��“����”��

���ͨ���Ҽ�����������Ƶ�“���”ѡ���ѡ��“ȫ������”�����������Զ���Դ�ļ�����������ȷ��������Ƶ�Ԫ����ȷ˳��

ͼ6.ʹ����ƹ����������ļ�

��ʼ������

�ɹ�������������Ҫ����Ƶ�Ԫ���ɳ�ʼ�����档�ڳ�ʼ��ģ��֮ǰ����ȷ����

����ѡ����Ƶ�Ԫ��

�����δѡ���κζ�����Ԫ�����������ģ�⣬ģ��������ʾ����ʾһ���Ի�����ѡ��һ����

Ҫ��ʼģ����̣��������“ģ��”������ѡ��“��ʼ��ģ��”����������������ģ�͵���ϸ˵���ͳ�ʼ�����ھ�����ƹ����У�ģ����������Ƶ�Ԫ���ڼ�����ڴ��й�������ģ�͡��ڳ�ʼ���ڼ䣬ģ���е����ж����ȡ���ʼֵ���������в�������ִ��һ�Σ�ֱ�������

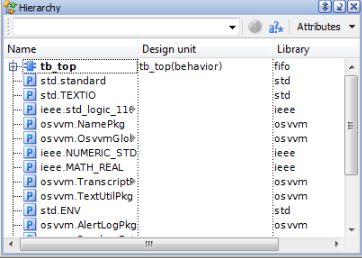

ͼ7.ģ�ⴰ��

ͼ8.��ʼ������

������ƽ̨����Ϊ������νṹ��ѡ�������“��νṹ”���ڡ�����ͼ��

ͼ9.��νṹ����

��ú��Ҽ���������ƽ̨ģ�鲢ѡ�����ӵ� |����ѡ����δ��ڽ���

������ͨ��ѡ������ѡ��������ģ�⡣ͨ�������ð�ť��ģ�⽫��ʼ���С�

ȫ������/����/����ֱ��ģ��

Ҫ��ģ��������ģ��һ��ʱ�䣬���ģ��˵���ѡ��“���ж���”ѡ�

Ҫ���ģ��Ự�����“ģ��”�˵���ѡ��“ֹͣģ��”��

��������������ģ�⣬��ģ��˵���ѡ������������

ͼ 10.����/ȫ������/����ֱ��ģ��

���β鿴��

����������в���������ܻῴ������������ļ��У�������ʾ��

ͼ 11.���β鿴��

Ҫ���沨���ļ���ʹ�õ�ǰ�������ý��в�����������ѡ���β˵�ѡ�

����

[1] ��Դ VHDL ��֤���� ��http://osvvm.org/��

[2] Github ��https://github.com/OSVVM/OSVVM��

��؟����

��Ӧ�ñʼ��е������ı�ժ���й����ṩ�Ŀ�Դ���ߵIJο����ϡ���Ӧ��˵��ּ�����Ϻ���֯���ݣ������ּĹ������̣����츣 Aldec �û�